- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376431 > UPD75206CW (NEC Corp.) 4-BIT SINGLE-CHIP MICROCOMPUTER PDF資料下載

參數(shù)資料

| 型號: | UPD75206CW |

| 廠商: | NEC Corp. |

| 英文描述: | 4-BIT SINGLE-CHIP MICROCOMPUTER |

| 中文描述: | 4位單片機 |

| 文件頁數(shù): | 25/62頁 |

| 文件大小: | 489K |

| 代理商: | UPD75206CW |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁

25

μ

PD75206

7.

STANDBY FUNCTIONS

Two standby modes (STOP mode and HALT mode) are available for the

μ

PD75206 to decrease power consump-

tion in the program standby mode.

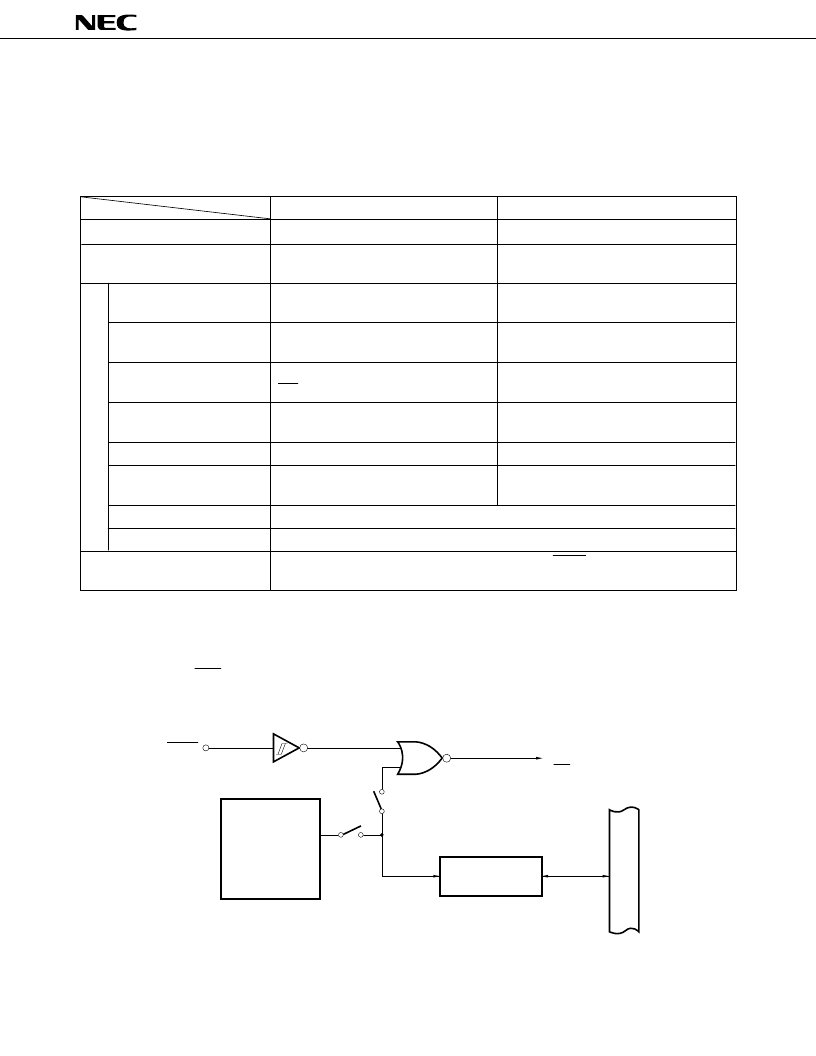

Table 7-1 Operation Status in Standby Mode

HALT Mode

HALT instruction

Setting enabled with either main system

clock or subsystem clock.

Stops only with CPU clock

Φ

(Oscillation

continued).

Operation (IRQBT set at reference time

intervals).

Operation enabled when serial clock other

than

Φ

is specified.

Operation enabled.

Operation enabled.

Operation enabled.

Set instruction

System clock when set

Clock oscillator

Basic interval timer

Serial interface

Timer/event counter

Timer/pulse generator

Watch timer

FIP controller/driver

CPU

STOP Mode

STOP instruction

Setting enabled only with main system

clock.

Oscillator stops only with main system

clock.

Operation stopped.

Operation enabled only when external

SCK input is selected for serial clock.

Operation enabled only when TI0 pin

input is specified for count clock.

Operation stopped.

Operation enabled only f

XT

is selected for

count clock.

O

Operation disabled (display off mode set before disabling).

Operation stopped.

Release signal

Interrupt request signal (except INT0, INT1, INT2) or RESET input enabled by

interrupt enable flag.

8.

RESET FUNCTIONS

The reset signal (RES) generator has a configuration shown in Fig.8-1.

Fig. 8-1 Reset Signal Generator

RESET

Power-On

Reset

Generator

Mask

Option

Internal Reset Signal

(RES)

Power-On Flag

(PONF)

I

Bit

Manipulation

Instruction

Execution

SWA

SWB

The power-on reset generator is a circuit to generate a one-shot pulse upon detection of the start-up of the power

voltage. This pulse is used in the three ways according to SWA, SWB mask option specification shown in Fig. 8-

1.

(

Refer to

10. MASK OPTION SELECTION.)

相關PDF資料 |

PDF描述 |

|---|---|

| UPD75208GF | 4-BIT SINGLE-CHIP MICROCOMPUTER |

| UPD75208 | 4-BIT SINGLE-CHIP MICROCOMPUTER |

| UPD75208CW | 4-BIT SINGLE-CHIP MICROCOMPUTER |

| UPD753208GT | 4-BIT SINGLE-CHIP MICROCONTROLLERS |

| UPD753204 | 4-BIT SINGLE-CHIP MICROCONTROLLERS |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| UPD75208 | 制造商:Panasonic Industrial Company 功能描述:IC |

| UPD753012AGC-P33-8BT-A | 制造商:Renesas Electronics Corporation 功能描述: |

| UPD753016AGC-P29-8BT | 制造商:Renesas Electronics Corporation 功能描述: |

| UPD75304GF-407-3B9 | 制造商:Renesas Electronics Corporation 功能描述: |

| UPD75306G182 | 制造商:Panasonic Industrial Company 功能描述:IC |

發(fā)布緊急采購,3分鐘左右您將得到回復。