- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359327 > V61C31161024 (Mosel Vitelic, Corp.) 64K x 16 HIGH SPEED STATIC RAM PDF資料下載

參數(shù)資料

| 型號(hào): | V61C31161024 |

| 廠商: | Mosel Vitelic, Corp. |

| 英文描述: | 64K x 16 HIGH SPEED STATIC RAM |

| 中文描述: | 64K的× 16高速靜態(tài)RAM |

| 文件頁數(shù): | 2/10頁 |

| 文件大小: | 83K |

| 代理商: | V61C31161024 |

2

V61C31161024 Rev. 0.5 August 1999

MOSEL V ITELIC

V61C31161024

Pin Descriptions

A

These 16 address inputs select one of the 64K x 16

bit segments in the RAM.

0

–A

15

Address Inputs

CE

CE is active LOW. It must be active to read from or

write to the device. If chip enable is not active, the

device is deselected and is in a standby power

mode. The I/O pins will be in the high-impedance

state when deselected.

Chip Enable Input

OE

The output enable input is active LOW. When OE

is Low with CE Low and WE High, data will be pre-

sented on the I/O pins. The I/O pins will be in the

high impedance state when OE is High.

Output Enable Input

UBE, LEB

Active low inputs. These inputs are used to enable

the upper or lower data byte.

Byte Enable

WE

The write enable input is active LOW and controls

read and write operations. With the chip enabled,

when WE is HIGH and OE is LOW, output data will

be present at the I/O pins; when WE is LOW and

OE is HIGH, the data present on the I/O pins will be

written into the selected memory locations.

Write Enable Input

I/O

These 16 bidirectional ports are used to read data

from and write data into the RAM.

0

–I/O

15

Data Input and Data Output Ports

V

CC

Power Supply

GND

Ground

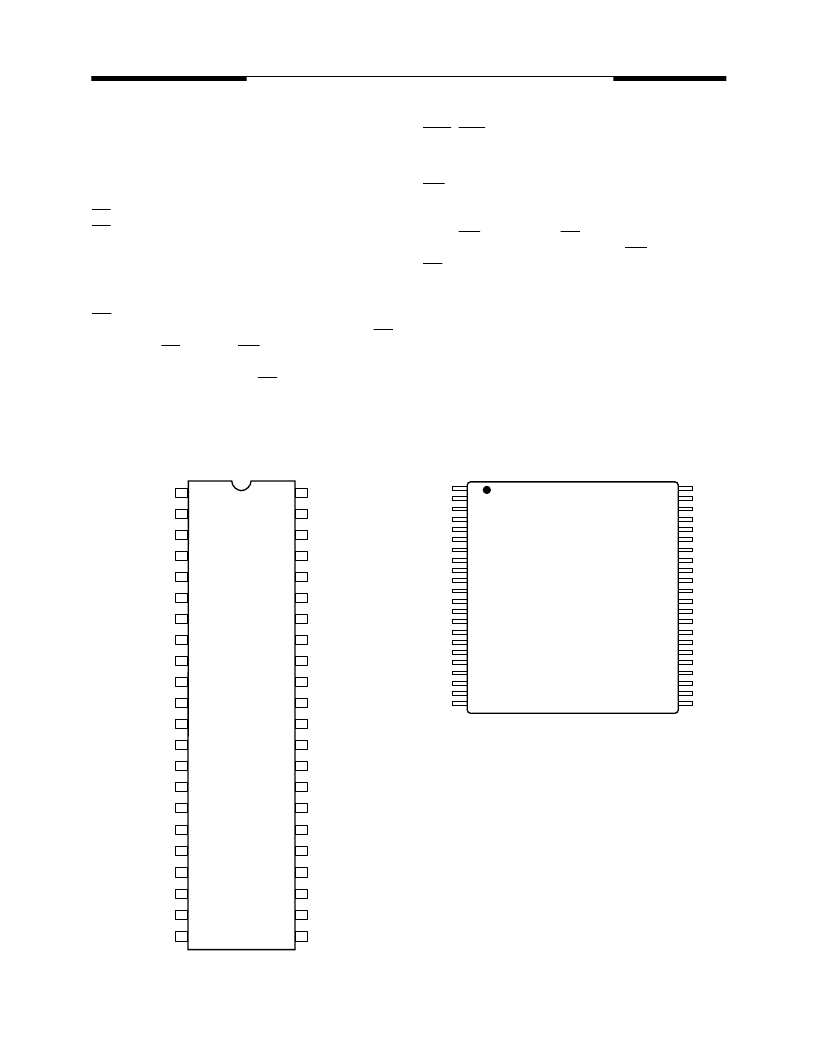

Pin Configurations (Top View)

44-Pin SOJ

44-Pin TSOP-II (Standard)

1

44

6131161024-02

2

43

3

42

4

41

5

40

6

39

7

38

8

37

9

36

10

35

11

34

12

33

13

32

14

31

15

30

16

29

A

3

A

2

A

1

A

0

CE

A

4

I/O

0

I/O

1

I/O

2

I/O

3

V

CC

GND

I/O

4

I/O

5

I/O

6

I/O

7

WE

A

6

A

7

OE

UBE

LBE

I/O

15

I/O

14

I/O

13

I/O

12

GND

V

CC

I/O

11

I/O

10

I/O

9

I/O

8

NC

17

28

A

15

A

14

A

13

A

12

NC

18

27

A

8

A

9

A

10

A

11

NC

19

26

20

25

21

24

22

23

A

5

A4

A3

A2

A1

A0

CE

I/O0

I/O1

I/O2

I/O3

VCC

GND

I/O4

I/O5

I/O6

I/O7

WE

A15

A14

A13

A12

NC

A5

A6

A7

OE

UBE

LBE

I/O15

I/O14

I/O13

I/O12

GND

VCC

I/O11

I/O10

I/O9

I/O8

NC

A8

A9

A10

A11

NC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

6131161024-03

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| V61C31161024-12T | 64K x 16 HIGH SPEED STATIC RAM |

| V61C3181024 | 128K X 8 HIGH SPEED STATIC RAM |

| V61C51161024 | 64K x 16 HIGH SPEED STATIC RAM |

| V61C5181024 | 128K X 8 HIGH SPEED STATIC RAM |

| V61C518256-10R | 32K X 8 HIGH SPEED STATIC RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| V61C31161024-12T | 制造商:MOSEL 制造商全稱:MOSEL 功能描述:64K x 16 HIGH SPEED STATIC RAM |

| V61C3181024 | 制造商:MOSEL 制造商全稱:MOSEL 功能描述:128K X 8 HIGH SPEED STATIC RAM |

| V61C32C120LI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 Dual-Port SRAM |

| V61C32C120LX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 Dual-Port SRAM |

| V61C32C120SI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 Dual-Port SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。