- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359339 > VC16241ADL (NXP SEMICONDUCTORS) 16-bit buffer/line driver 3-State PDF資料下載

參數(shù)資料

| 型號: | VC16241ADL |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 通用總線功能 |

| 英文描述: | 16-bit buffer/line driver 3-State |

| 中文描述: | LVC/LCX/Z SERIES, QUAD 4-BIT DRIVER, TRUE OUTPUT, PDSO48 |

| 封裝: | 7.50 MM, PLASTIC, MO-118AA, SOT-370-1, SSOP3-48 |

| 文件頁數(shù): | 2/10頁 |

| 文件大?。?/td> | 78K |

| 代理商: | VC16241ADL |

Philips Semiconductors

Product specification

74LVC16241A

16-bit buffer/line driver (3-State)

2

1997 Jul 29

853-2006 18217

FEATURES

5 volt tolerant inputs/outputs for interfacing with 5V logic

Wide supply voltage range of 1.2V to 3.6V

Complies with JEDEC standard no. 8-1A

CMOS low power consumption

MULTIBYTE

TM

flow-through standard pin-out architecture

Low inductance multiple power and ground pins for minimum

noise and ground bounce

Direct interface with TTL levels

DESCRIPTION

The 74LVC16241A is a high-performance, low-power, low-voltage,

Si-gate CMOS device, superior to most advanced CMOS

compatible TTL families. Inputs can be driven from either 3.3V or 5V

devices. In 3-State operation, outputs can handle 5V. These

features allow the use of these devices in a mixed 3.3V/5V

environment.

The 74LVC16241A is a 16-bit buffer/line driver with 3-State outputs.

The 3-State outputs are controlled by the output enable inputs nOE

and nOE. Schmitt-trigger action at all inputs makes the circuit highly

tolerant for slower input rise and fall times. The device can be used

as four 4-bit buffers, two 8-bit buffers or one 16-bit buffer.

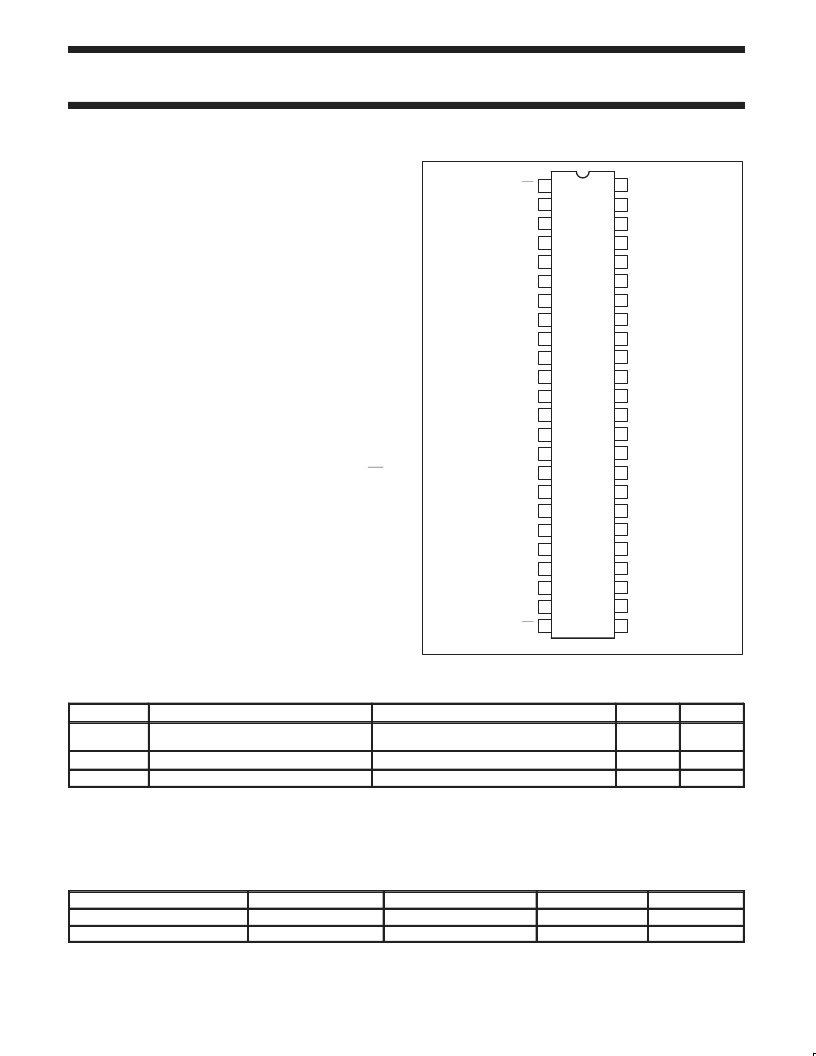

PIN CONFIGURATION

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

1OE

1Y0

1Y1

GND

1Y2

1Y3

V

CC

2Y1

GND

2Y2

2Y3

3Y0

3Y1

GND

2Y0

3Y2

3Y3

V

CC

4Y0

4Y1

4A1

4A0

V

CC

3A3

3A2

GND

3A1

3A0

2A3

2A2

GND

2A1

2A0

V

CC

1A3

1A2

GND

1A1

1A0

2OE

21

22

23

24

25

26

27

28

GND

4Y2

4Y3

4OE

3OE

4A3

4A2

GND

SW00049

QUICK REFERENCE DATA

GND = 0 V; T

amb

= 25 C; t

r

= t

f

SYMBOL

2.5 ns

PARAMETER

CONDITIONS

TYPICAL

UNIT

t

PHL

/t

PLH

Propagation delay

nAn to nYn

C

L

= 50pF

V

CC

= 3.3V

2.9

ns

C

I

C

PD

Input capacitance

5.0

pF

Power dissipation capacitance per buffer

V

I

= GND to V

CC1

25

pF

NOTES:

1. C

PD

is used to determine the dynamic power dissipation (P

D

in W):

P

D

= C

PD

x V

CC2

x f

i

+ (C

L

x V

CC2

x f

o

) where:

f

i

= input frequency in MHz; C

L

= output load capacity in pF;

f

o

= output frequency in MHz; V

CC

= supply voltage in V;

(C

L

x V

CC2

x f

o

) = sum of outputs.

ORDERING INFORMATION

PACKAGES

48-Pin Plastic SSOP Type III

48-Pin Plastic TSSOP Type II

TEMPERATURE RANGE

–40

°

C to +85

°

C

–40

°

C to +85

°

C

OUTSIDE NORTH AMERICA

74LVC16241A DL

74LVC16241A DGG

NORTH AMERICA

VC16241A DL

VC16241A DGG

DWG NUMBER

SOT370-1

SOT362-1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VC2-1 | CAPSULE ANTI CORROSION |

| VC2-2 | CAPSULE ANTI CORROSION |

| VC1-1 | CAPSULE ANTI CORROSION |

| VC20-SERIES | Peripheral IC |

| VC50-SERIES | Peripheral IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VC16244ADGG | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:16-bit buffer/line driver; 5V input/output tolerant 3-State |

| VC16244ADL | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:16-bit buffer/line driver; 5V input/output tolerant 3-State |

| VC16245ADGG | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:16-bit bus transceiver with direction pin; 5V tolerant 3-State |

| VC16245ADL | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:16-bit bus transceiver with direction pin; 5V tolerant 3-State |

| VC16373ADGG | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:16-bit D-type transparent latch with 5 Volt tolerant inputs/outputs 3-State |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。