- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359423 > VS133-R512 (Electronic Theatre Controls, Inc.) Memory Module PDF資料下載

參數(shù)資料

| 型號: | VS133-R512 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Memory Module |

| 中文描述: | 內(nèi)存模塊 |

| 文件頁數(shù): | 5/7頁 |

| 文件大小: | 124K |

| 代理商: | VS133-R512 |

VS133-R512

PDRB-28998-X045-01

Buffalo Technology

(5/7)

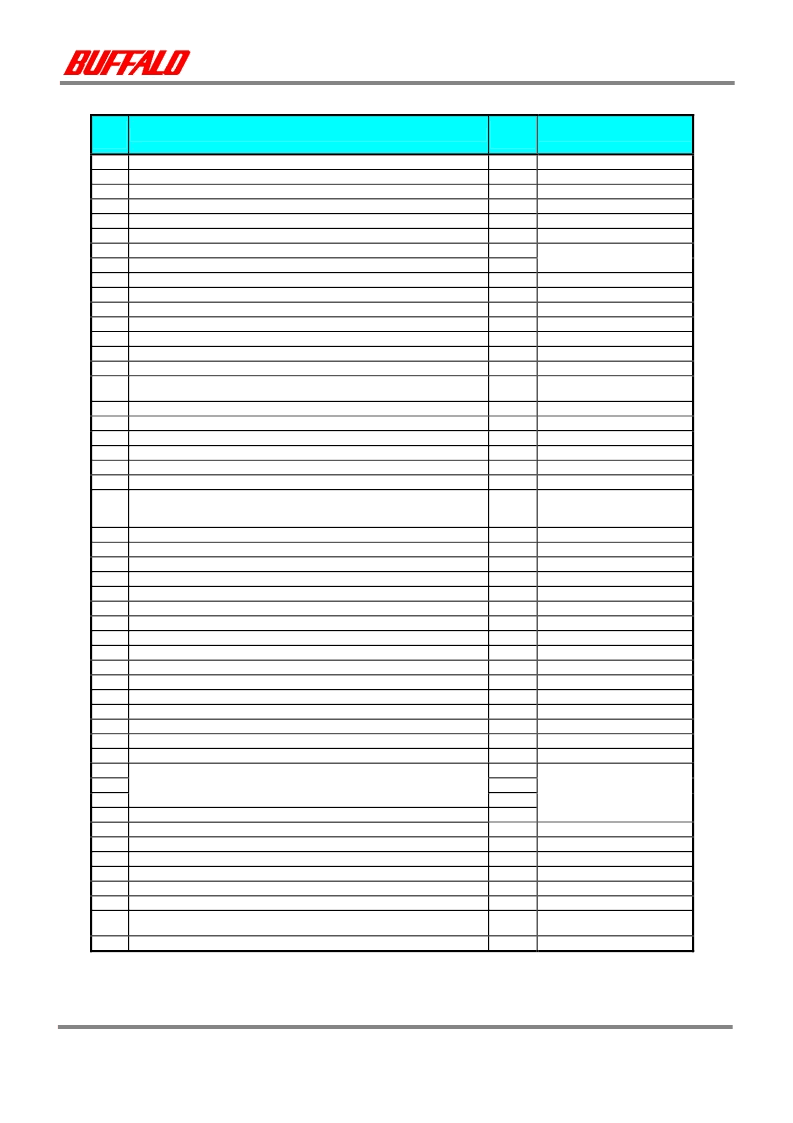

6. Serial Presence Detect (SPD) Data Structure

Byte

No.

Function

Hex

Value

Function Supported

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

Defines # of bytes written into serial memory at module manufacturer

Total # of bytes of SPD memory device

Fundamental memory type (FPM, EDO, SDRAM..)

# of row addresses on this assembly

# Column Addresses on this assembly

# Module Banks on this assembly

Data Width of this assembly

... Data Width continuation

Voltage interface standard of this assembly

SDRAM Cycle time (highest CAS latency)

SDRAM Access from Clock (highest CAS latency)

DIMM Configuration type (non-parity, ECC)

Refresh Rate/Type

Primary SDRAM Width

Error Checking SDRAM width

Minimum Clock Delay

Back to Back Random Column Address

Burst Lengths Supported

# of Banks on Each SDRAM Device

CAS# Latency

CS# Latency

Write Latency

SDRAM Module Attributes

80

08

04

0D

0A

02

48

00

01

75

54

02

82

08

08

128Bytes

256Bytes

SDR SDRAM

13

10

2Banks

72bits

LVTTL

7.5ns (CL=3)

5.4ns (CL =3)

ECC

7.8μs

x8bit

x8bit

15

01

1CLK

16

17

18

19

20

21

8F

04

06

01

01

1F

Burst Lengths (1,2,4,8,FULL)

4Banks

CAS Latency =2,3

CS Latency =0

WE Latency =0

Registered with PLL

Supports Write1/Read Burst

Supports Precharge All

Supports Auto-Precharge

10ns (CL=2)

6ns (CL=2)

Non Support

Non Support

20ns

15ns

20ns

45ns

256MB

1.5ns

0.8ns

1.5ns

0.8ns

Undefined

Rev 1.2

Checksum

22

SDRAM Device Attributes: General

0E

23

24

25

26

27

28

29

30

31

32

33

34

35

SDRAM Cycle time (2nd highest CAS latency)

SDRAM Access from Clock (2nd highest CAS latency)

SDRAM Cycle time (3rd highest CAS latency)

SDRAM Access from Clock (3rd highest CAS latency)

Minimum Row Precharge Time

Row Activate to Row Activate Min.

RAS to CAS Delay Min

Minimum RAS Pulse Width

Density of each bank on module

Command and Address signal input setup time

Command and Address signal input hold time

Data signal input setup time

Data signal input hold time

36-61 Superset Information (may be used in future)

62

SPD Data Revision Code

63

Checksum for bytes 0-62

64-66

67

68-71

72

Manufacturing Location

73-90 Manufacturer’s Part Number

91-92 Revision Code

93-94 Manufacturing Date

95-98 Assembly Serial Number

99-125 Manufacturer Specific Data

126 Intel specification frequency

A0

60

00

00

14

0F

14

2D

40

15

08

15

08

00

12

04

7F

83

00

01

20

00

00

00

00

64

Manufacturer’s JEDEC ID code per JEP-108E

MELCO inc.

Blank

Undefined

Undefined

Undefined

Undefined

100MHz Compatible

Clock=0

CL =2,3

Undefined

127 Intel Specification CAS# Latency support

87

128+ Unused storage locations

00

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VS19 | Interface IC |

| VS20 | Interface IC |

| VS2120QE | OBSERVATION SYSTEM B/W |

| VS21 | Interface IC |

| VS22 | Interface IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VS1340-01-01 | 制造商:Vivid Semiconductors 功能描述:ELECTRONIC COMPONENT |

| VS134A | 制造商:Aten International 功能描述: |

| VS138A | 制造商:Aten International 功能描述:Bulk |

| VS1-4 | 制造商:Greenlee Textron Inc 功能描述:SPLITTER 4WAY 1GHZ |

| VS-141A | 制造商:Actionstar 功能描述:4 Way VGA Switch 制造商:ACTIONSTAR 功能描述:4 WAY ELECTRONIC VGA SWITCH |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。