- 您現在的位置:買賣IC網 > PDF目錄231497 > W3EG264M64EFSU335D4-SG (MICROSEMI CORP-PMG MICROELECTRONICS) 128M X 64 DDR DRAM MODULE, 0.7 ns, DMA200 PDF資料下載

參數資料

| 型號: | W3EG264M64EFSU335D4-SG |

| 廠商: | MICROSEMI CORP-PMG MICROELECTRONICS |

| 元件分類: | DRAM |

| 英文描述: | 128M X 64 DDR DRAM MODULE, 0.7 ns, DMA200 |

| 封裝: | ROHS COMPLIANT, SO-DIMM-200 |

| 文件頁數: | 7/11頁 |

| 文件大小: | 190K |

| 代理商: | W3EG264M64EFSU335D4-SG |

W3EG264M64EFSU-D4

5

White Electronic Designs Corporation (602) 437-1520 www.wedc.com

White Electronic Designs

August 2005

Rev. 0

ADVANCED

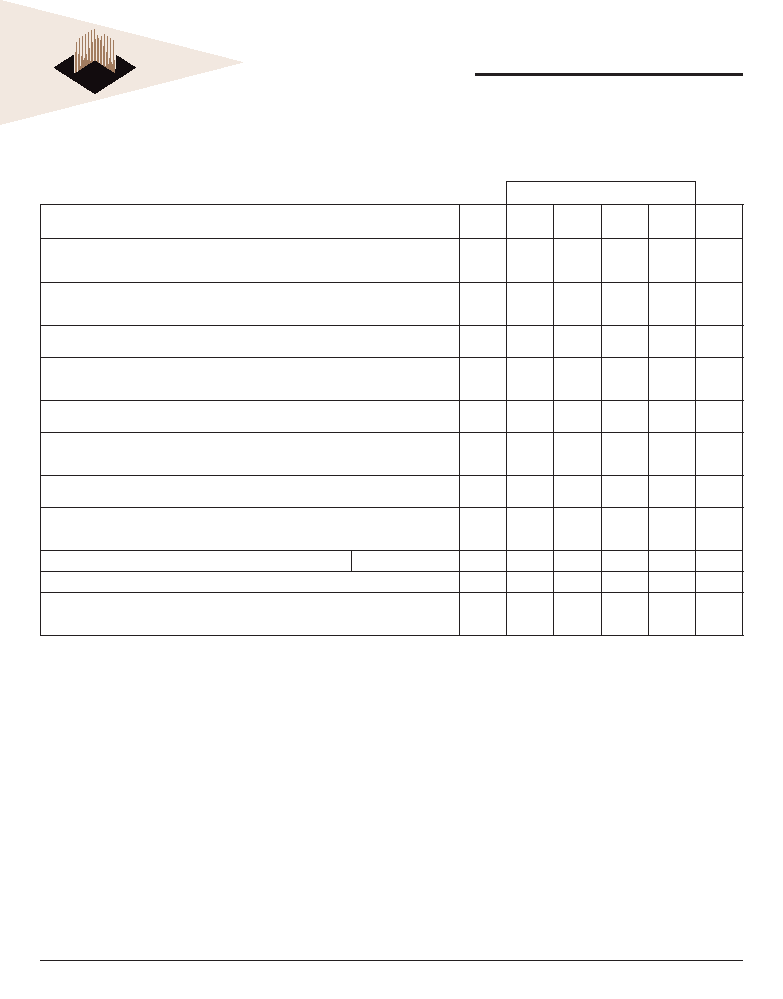

IDD SPECIFICATIONS AND CONDITIONS

0°C ≤ TA ≤ +70°C; VCC, VCCQ = +2.5V ±0.2V

DDR400: VCC = VCCQ = +2.6V ±0.2V

MAX

PARAMETER/CONDITION

SYM

DDR400

@CL=3

DDR333

@CL=2.5

DDR266

@CL=2

DDR266

@CL=2.5

UNITS

OPERATING CURRENT: One device bank; Active-Precharge; tRC = tRC (MIN); tCK = tCK

(MIN); DQ, DM and DQS inputs changing once per clock cycle; Address and control inputs

changing once every two clock cycles

IDD0

2475

2070

1845

mA

OPERATING CURRENT: One device bank; Active-Read-Precharge; Burst = 4; tRC = tRC

(MIN); tCK = tCK (MIN); IOUT = 0mA; Address and control inputs changing once per clock

cycle

IDD1

2745

2340

2115

mA

PRECHARGE POWER-DOWN STANDBY CURRENT: All device banks idle; Power-down

mode; tCK = tCK (MIN); CKE = (LOW)

IDD2P

90

mA

IDLE STANDBY CURRENT: CS# = HIGH; All device banks are idle; tCK = tCK (MIN); CKE =

HIGH; Address and other control inputs changing once per clock cycle. VIN = VREF for DQ,

DQS, and DM

IDD2F

990

810

720

mA

ACTIVE POWER-DOWN STANDBY CURRENT: One device bank active; Power-down

mode; tCK = tCK (MIN); CKE = LOW

IDD3P

810

630

540

mA

ACTIVE STANDBY CURRENT: CS# = HIGH; CKE = HIGH; One device bank active; tRC =

tRAS (MAX); tCK = tCK (MIN); DQ, DM and DQS inputs changing twice per clock cycle; Address

and other control inputs changing once per clock cycle

IDD3N

1080

900

810

mA

OPERATING CURRENT: Burst = 2; Reads; Continuous burst; One device bank active;

Address and control inputs changing once per clock cycle; tCK = tCK (MIN); IOUT = 0mA

IDD4R

2790

2385

2115

mA

OPERATING CURRENT: Burst = 2; Writes; Continuous burst; One device bank active;

Address and control inputs changing once per clock cycle; tCK = tCK (MIN); DQ, DM, and DQS

inputs changing twice per clock cycle

IDD4W

2790

2295

2025

mA

AUTO REFRESH BURST CURRENT:

tREFC = tRFC (MIN)

IDD5

4185

3510

3330

mA

SELF REFRESH CURRENT: CKE ≤ 0.2V

IDD6

90

mA

OPERATING CURRENT: Four device bank interleaving READs (Burst = 4) with auto

precharge, tRC = minimum tRC allowed; tCK = tCK (MIN); Address and control inputs change

only during Active READ, or WRITE commands

IDD7

5130

4545

3960

mA

相關PDF資料 |

PDF描述 |

|---|---|

| W3EG7262S262D3 | DDR DRAM MODULE, DMA184 |

| W7NCF08GH10CS7AM1G | FLASH 3.3V PROM MODULE, XMA50 |

| W7NCF08GH10CSA3BM1G | FLASH 3.3V PROM MODULE, XMA50 |

| W7NCF08GH10IS8DM1G | FLASH 3.3V PROM MODULE, XMA50 |

| W7NCF08GH10IS9DM1G | FLASH 3.3V PROM MODULE, XMA50 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| W3EG264M64EFSU335D4-X | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:1GB - 2x64Mx64 DDR SDRAM, UNBUFFERED, FBGA |

| W3EG264M64EFSU403D4-X | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:1GB - 2x64Mx64 DDR SDRAM, UNBUFFERED, FBGA |

| W3EG264M64EFSU-D4 | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:1GB - 2x64Mx64 DDR SDRAM, UNBUFFERED, FBGA |

| W3EG264M64EFSUXXXD4-MG | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:1GB - 2x64Mx64 DDR SDRAM, UNBUFFERED, FBGA |

| W3EG264M64EFSUXXXD4-SG | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:1GB - 2x64Mx64 DDR SDRAM, UNBUFFERED, FBGA |

發(fā)布緊急采購,3分鐘左右您將得到回復。