- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄202138 > W3H128M72E0400SBM (WHITE ELECTRONIC DESIGNS CORP) DDR DRAM, PBGA208 PDF資料下載

參數(shù)資料

| 型號: | W3H128M72E0400SBM |

| 廠商: | WHITE ELECTRONIC DESIGNS CORP |

| 元件分類: | DRAM |

| 英文描述: | DDR DRAM, PBGA208 |

| 封裝: | 16 X 22 MM, 1 MM PITCH, PBGA-208 |

| 文件頁數(shù): | 10/31頁 |

| 文件大小: | 993K |

| 代理商: | W3H128M72E0400SBM |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁

W3H128M72E-XSBX

18

White Electronic Designs Corporation (602) 437-1520 www.whiteedc.com

White Electronic Designs

December 2008

Rev. 4

White Electronic Designs Corp. reserves the right to change products or specications without notice.

READ COMMAND

The READ command is used to initiate a burst read access

to an active row. The value on the BA2–BA0 inputs selects

the bank, and the address provided on inputs A0–i (where

i = A9) selects the starting column location. The value on

input A10 determines whether or not auto precharge is

used. If auto precharge is selected, the row being accessed

will be precharged at the end of the READ burst; if auto

precharge is not selected, the row will remain open for

subsequent accesses.

READ OPERATION

READ bursts are initiated with a READ command. The

starting column and bank addresses are provided with the

READ command and auto precharge is either enabled or

disabled for that burst access. If auto precharge is enabled,

the row being accessed is automatically precharged at the

completion of the burst. If auto precharge is disabled, the

row will be left open after the completion of the burst.

During READ bursts, the valid data-out element from the

starting column address will be available READ latency

(RL) clocks later. RL is dened as the sum of AL and CL;

RL = AL + CL. The value for AL and CL are programmable

via the MR and EMR commands, respectively. Each

subsequent data-out element will be valid nominally at

the next positive or negative clock edge (i.e., at the next

crossing of CK and CK#).

DQS/DQS# is driven by the DDR2 SDRAM along with

output data. The initial LOW state on DQS and HIGH state

on DQS# is known as the read preamble (tRPRE). The LOW

state on DQS and HIGH state on DQS# coincident with

the last data-out element is known as the read postamble

(tRPST).

Upon completion of a burst, assuming no other commands

have been initiated, the DQ will go High-Z.

Data from any READ burst may be concatenated with

data from a subsequent READ command to provide a

continuous ow of data. The rst data element from the

new burst follows the last element of a completed burst.

The new READ command should be issued x cycles after

the rst READ command, where x equals BL / 2 cycles.

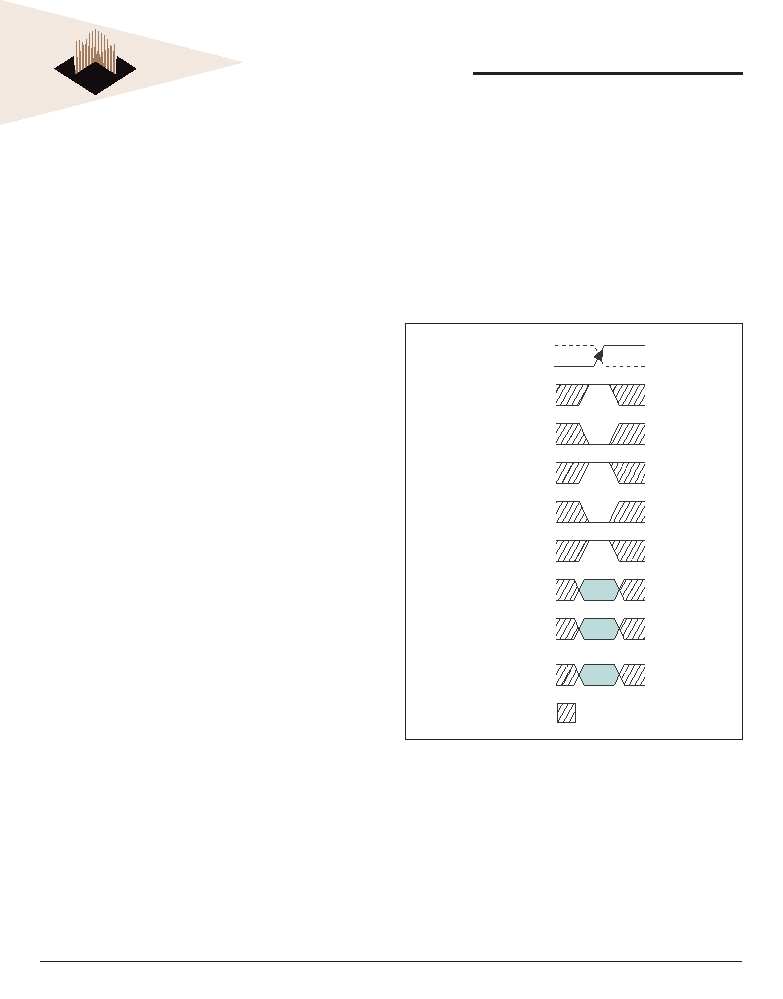

FIGURE 11 – READ COMMAND

DON’T CARE

CK

CK#

CS#

RAS#

CAS#

WE#

CKE

Col

Bank

ADDRESS

BANK ADDRESS

AUTO PRECHARGE

ENABLE

DISABLE

A10

相關PDF資料 |

PDF描述 |

|---|---|

| W3DG6465V7D1 | 64M X 64 SYNCHRONOUS DRAM MODULE, ZMA144 |

| W7NCF01GH10CS5AG | 64M X 16 FLASH 3.3V PROM CARD, 150 ns, UUC |

| W7NCF01GH10IS2FG | 64M X 16 FLASH 3.3V PROM CARD, 150 ns, UUC |

| W7NCF01GH20CS5AG | 64M X 16 FLASH 3.3V PROM CARD, 150 ns, UUC |

| W7NCF01GH20CS7BG | 64M X 16 FLASH 3.3V PROM CARD, 150 ns, UUC |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| W3H128M72E-400SBC | 制造商:Microsemi Corporation 功能描述:128M X 72 DDR2, 1.8V, 400MHZ, 208PBGA COMMERICAL TEMP. - Bulk |

| W3H128M72E-400SBI | 制造商:Microsemi Corporation 功能描述:128M X 72 DDR2, 1.8V, 400MHZ, 208PBGA INDUSTRIAL TEMP. - Bulk 制造商:Microsemi Corporation 功能描述:SDRAM MEMORY |

| W3H128M72E-400SBM | 制造商:Microsemi Corporation 功能描述:128M X 72 DDR2, 1.8V, 400MHZ, 208PBGA MIL-TEMP. - Bulk 制造商:Microsemi Corporation 功能描述:SDRAM MEMORY |

| W3H128M72E-533NBI | 制造商:Microsemi Corporation 功能描述:128M X 72 DDR2, 1.8V, 533MHZ, 208PBGA IND TEMP. - Bulk |

| W3H128M72E-533SBC | 制造商:Microsemi Corporation 功能描述:128M X 72 DDR2, 1.8V, 533MHZ, 208PBGA COMMERICAL TEMP. - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。