- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361790 > W65C832PL-4 32-Bit Microprocessor PDF資料下載

參數(shù)資料

| 型號(hào): | W65C832PL-4 |

| 元件分類: | 32位微控制器 |

| 英文描述: | 32-Bit Microprocessor |

| 中文描述: | 32位微處理器 |

| 文件頁(yè)數(shù): | 22/62頁(yè) |

| 文件大小: | 891K |

| 代理商: | W65C832PL-4 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)當(dāng)前第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)

WESTERN DESIGN CENTER

W65C816S

March 1, 2000

22

3.5.12

The second and third bytes of the instruction are added to the X Index Register to form the low-order 16-bits of the

effective address. The Data Bank Register contains the high-order 8 bits of the effective address.

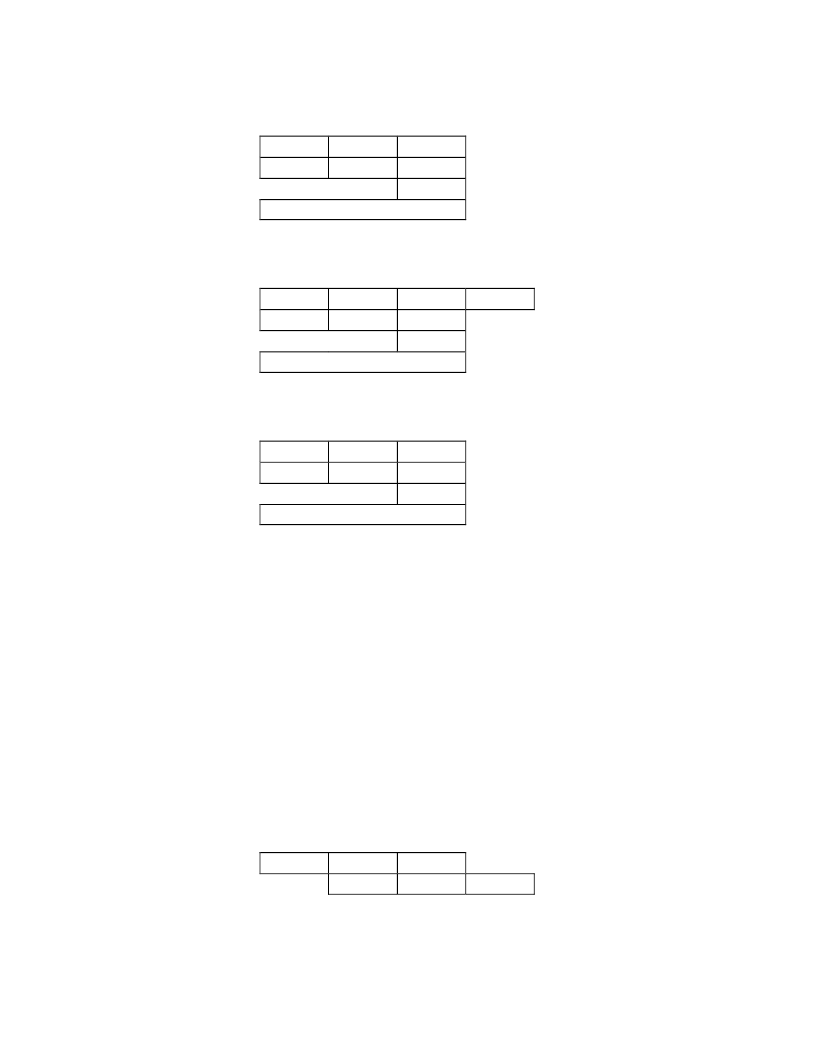

Absolute Indexed With X-a,x

Instruction:

OpCo

DBR

addrl

addrh

addrh

addrl

X Reg

+

Operand

effective address

3.5.13

The second, third and fourth bytes of the instruction form a 24-bit base address. The effective address is the sum of

this 24-bit address and the X Index Register.

Absolute Long Indexed With X-al,x

Instruction:

OpCo

baddr

addrl

addrh

addrh

addrl

X Reg

baddr

+

Operand

effective address

3.5.14

The second and third bytes of the instruction are added to the Y Index Register to form the low-order 16 bits of the

effective address. The Data Bank Register contains the high-order 8 bits of the effective address.

Absolute Indexed With Y-a,y

Instruction:

OpCo

DBR

addrl

addrh

addrh

addrl

Y Reg

+

Operand

effective address

3.5.15

This address mode, referred to as Relative Addressing, is used only with the Branch instructions. If the condition

being tested is met, the second byte of the instruction is added to the Program Counter, which has been updated to

point to the OpCode of the next instruction. The offset is a signed 8-bit quantity in the range from -128 to 127. The

Program Bank Register is not affected.

Program Counter Relative-r

3.5.16

This address mode, referred to as Relative Long Addressing, is used only with the Unconditional Branch Long

instruction (BRL) and the Push Effective Relative instruction (PER). The second and third bytes of the instruction

are added to the Program Counter, which has been updated to point to the OpCode of the next instruction. With the

branch instruction, the Program Counter is loaded with the result. With the Push Effective Relative instruction, the

result is stored on the stack. The offset is a signed 16-bit quantity in the range from -32768 to 32767. The Program

Bank Register is not affected.

Program Counter Relative Long-rl

3.5.17

The second and third bytes of the instruction form an address to a pointer in Bank 0. The Program Counter is

loaded with the first and second bytes at this pointer. With the Jump Long (JML) instruction, the Program Bank

Register is loaded with the third byte of the pointer.

Absolute Indirect-(a)

Instruction:

Indirect Address:

OpCode

addrl

00

addrh

addrh

addrl

New PC = (indirect address)

with JML:

New PC = (indirect address)

New PBR = (indirect address +2)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| W65C832PL-6 | 32-Bit Microprocessor |

| W65C832PL-8 | 32-Bit Microprocessor |

| W65C90P-4 | Magnitude Comparator |

| W65C90P-6 | Magnitude Comparator |

| W65C90P-8 | Magnitude Comparator |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| W65C832PL-6 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| W65C832PL-8 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| W65C832PL-E | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ADVANCED CMOS DESIGN FOR LOW POWER POWER CONSUMPTION AND INCREASED NOISE IMMUNITY |

| W65C90P-4 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Magnitude Comparator |

| W65C90P-6 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Magnitude Comparator |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。