- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371190 > X1243V8 (INTERSIL CORP) Real Time Clock/Calendar/Alarm with EEPROM PDF資料下載

參數(shù)資料

| 型號: | X1243V8 |

| 廠商: | INTERSIL CORP |

| 元件分類: | XO, clock |

| 英文描述: | Real Time Clock/Calendar/Alarm with EEPROM |

| 中文描述: | 1 TIMER(S), REAL TIME CLOCK, PDSO8 |

| 封裝: | PLASTIC, TSSOP-8 |

| 文件頁數(shù): | 2/18頁 |

| 文件大小: | 90K |

| 代理商: | X1243V8 |

X1243

2

PIN DESCRIPTIONS

Serial Clock (SCL)

The SCL input is used to clock all data into and out of

the device. The input buffer on this pin is always active

(not gated).

Serial Data (SDA)

SDA is a bidirectional pin used to transfer data into

and out of the device. It has an open drain output and

may be wire ORed with other open drain or open col-

lector outputs. The input buffer is always active (not

gated).

An open drain output requires the use of a pull-up

resistor. The output circuitry controls the fall time of

the output signal with the use of a slope controlled

pull-down. The circuit is designed for 400kHz 2-wire

interface speeds.

V

BACK

This input provides a backup supply voltage to the

device. V

BACK

supplies power to the device in the

event the V

CC

supply fails.

Interrupt Output— IRQ

This is an interrupt signal output. This signal notifies a

host processor that alarm has occurred and requests

action. It is an open drain active LOW output.

X1, X2

The X1 and X2 pins are the input and output, respec-

tively, of an inverting amplifier that can be configured

for use as an on-chip oscillator. A 32.768kHz quartz

crystal is used. Recommeded crystals are Sieko VT-200

or Epson C-002RX. The crystal supplies a timebase

for a clock/oscillator. The internal clock can be driven

by an external signal on X1, with X2 left unconnected.

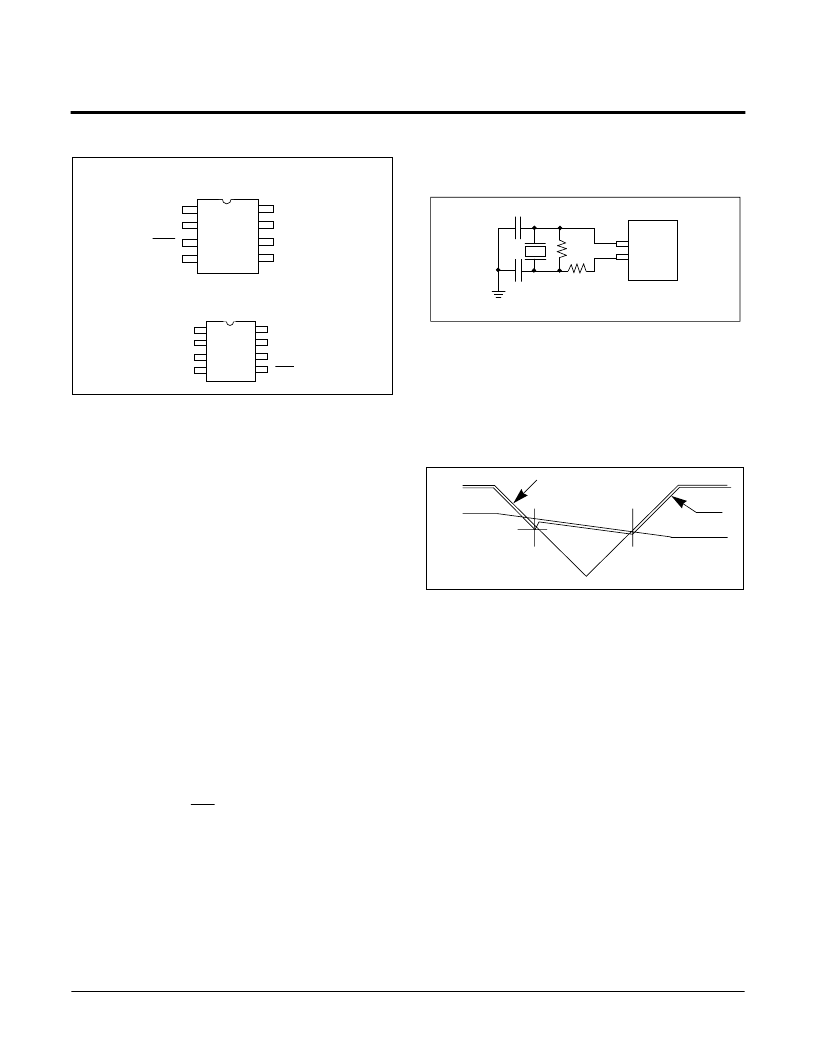

Figure 1. Recommended Crystal connection

POWER CONTROL OPERATION

The Power control circuit accepts a V

input. The power control circuit will switch to V

when V

CC

< V

BACK

- 0.2V. It will switch back to V

when V

CC

exceeds V

BACK

CC

and a V

BACK

BACK

CC

.

Figure 2. Power Control

REAL TIME CLOCK OPERATION

The Real Time Clock (RTC) uses an external, 32.768KHz

quartz crystal to maintain an accurate internal repre-

sentation of the year, month, day, date, hour, minute,

and seconds. The RTC has leap-year correction and a

century byte. The clock will also correct for months hav-

ing fewer than 31 days and will have a bit that controls

24 hour or AM/PM format. When the X1243 powers up

after the loss of both V

CC

and V

increment until at least one byte is written to the clock

register.

BACK

, the clock will not

Reading the Real Time Clock

The RTC is read by initiating a Read command and

specifying the address corresponding to the register of

the Real Time Clock. The RTC Registers can then be

read in a Sequential Read Mode. Since the clock runs

continuously and a read takes a finite amount of time,

there is the possibility that the clock could change dur-

ing the course of a read operation. In this device, the

time is latched by the read command (falling edge of

X1243

8 pin TSSOP

X1

X2

V

Back

V

CC

IRQ

SCL

SDA

V

SS

1

2

3

4

7

6

5

8

X1243

X1

X2

V

Back

SCL

SDA

V

CC

IRQ

V

SS

1

2

3

4

7

6

5

8

8 pin SOIC

X1

X2

43pF

18pF

220K

10M

V

BACK

V

CC

= V

BACK

-0.2V

Internal

Voltage

V

CC

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X125-55FA | 30V Single N-Channel HEXFET Power MOSFET in a TO-220AB package; Similar to the IRF3703 with Lead-Free Packaging. |

| X125-56FA | 30V Single N-Channel HEXFET Power MOSFET in a TO-262 package; Similar to IRF3708L with Lead Free Packaging |

| X125-57FA | BEACON STATIC 12VDC |

| X125-58FA | BEACON STATIC 24VDC |

| X1288S16-4.5A | RTC Module With CPU Supervisor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X-1244 | 制造商:Pulse 功能描述:TRANSFORMERS - Rail/Tube |

| X124K | 制造商:IQD Frequency Products 功能描述:CRYSTAL OSCILLATOR 8.192000MHZ |

| X124LE0 | 制造商:SENSORTECHNICS 制造商全稱:Sensortechnics GmbH 功能描述:8 mm switching soleniod valves |

| X124LEB | 制造商:SENSORTECHNICS 制造商全稱:Sensortechnics GmbH 功能描述:8 mm switching soleniod valves |

| X124LF0 | 制造商:SENSORTECHNICS 制造商全稱:Sensortechnics GmbH 功能描述:8 mm switching soleniod valves |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。