- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄371197 > X24001PM Identi⑩PROM PDF資料下載

參數(shù)資料

| 型號(hào): | X24001PM |

| 英文描述: | Identi⑩PROM |

| 中文描述: | 認(rèn)⑩胎膜早破 |

| 文件頁(yè)數(shù): | 5/13頁(yè) |

| 文件大?。?/td> | 47K |

| 代理商: | X24001PM |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)當(dāng)前第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)

X24001

5

Read Operation

The byte read operation is initiated with a start condition.

The start condition is followed by an eight-bit control byte

which consists of a two-bit read command (1,0), four

address bits, and two “don’t care” bits. After receipt of

the control byte, the X24001 will enter the read mode

and transfer data into the shift register from the array.

This data is shifted out of the device on the next eight

SCL clocks. At the end of the read, all counters are reset

and the X24001 will enter the standby mode. As with a

write, the read operation can be interrupted by a start or

stop condition while the command or address is being

clocked in. While clocking data out, starts or stops

cannot be generated.

During the second don’t care clock cycle, starts and

stops are ignored. The master must free the bus prior to

the end of this clock cycle to allow the X24001 to begin

outputting data (Figures 4 and 5).

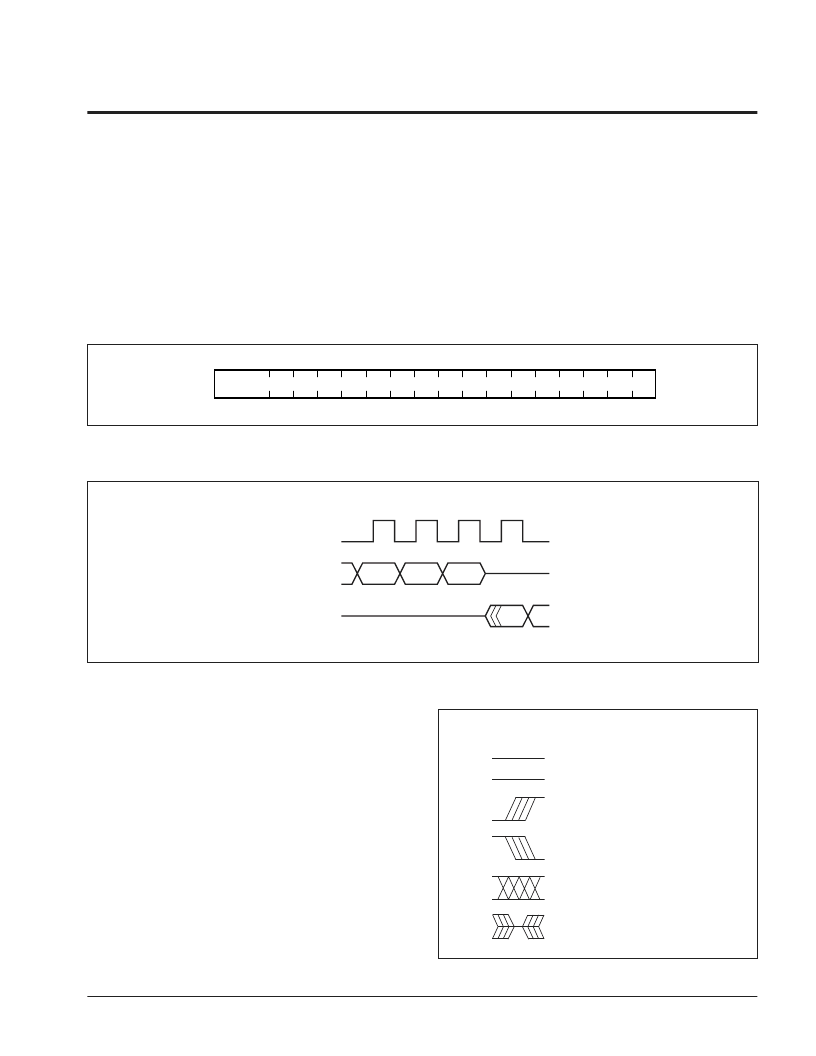

3830 FHD F07

Figure 4. Read Sequence

3830 FHD F06

Figure 5. Read Cycle Timing

6

7

8

1

SDA IN

SCK

SDA OUT

A0

XX

XX

D7

D6

START

1

0

A3

A2

A1

A0

XX XX D7

D6

D5

D4

D3

D2

D1

D0

SYMBOL TABLE

WAVEFORM

INPUTS

OUTPUTS

Must be

steady

Will be

steady

May change

from LOW

to HIGH

Will change

from LOW

to HIGH

May change

from HIGH

to LOW

Will change

from HIGH

to LOW

Don’t Care:

Changes

Allowed

N/A

Changing:

State Not

Known

Center Line

is High

Impedance

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X24001PM-2.7 | Identi⑩PROM |

| X24001PM-3 | Identi⑩PROM |

| X24001S | Identi⑩PROM |

| X24001SI | Identi⑩PROM |

| X24001SM | Identi⑩PROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X24001PM-2.7 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Identi⑩PROM |

| X24001PM-3 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Identi⑩PROM |

| X24001S | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Identi⑩PROM |

| X24001S-2.7 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Identi⑩PROM |

| X24001S-3 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Identi⑩PROM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。