- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371201 > X24325SI Voltage Regulator IC; Package/Case:5-SOT-23; Supply Voltage Max:15V; Leaded Process Compatible:Yes; Output Voltage Max:15V; Packaging:Cut Tape; Peak Reflow Compatible (260 C):Yes; Number of Channels:4; Source Output Current Max:40mA PDF資料下載

參數(shù)資料

| 型號(hào): | X24325SI |

| 英文描述: | Voltage Regulator IC; Package/Case:5-SOT-23; Supply Voltage Max:15V; Leaded Process Compatible:Yes; Output Voltage Max:15V; Packaging:Cut Tape; Peak Reflow Compatible (260 C):Yes; Number of Channels:4; Source Output Current Max:40mA |

| 中文描述: | 先進(jìn)的2線串行e的2座門鎖TM保護(hù)胎膜早破 |

| 文件頁數(shù): | 7/17頁 |

| 文件大小: | 79K |

| 代理商: | X24325SI |

X24325

7

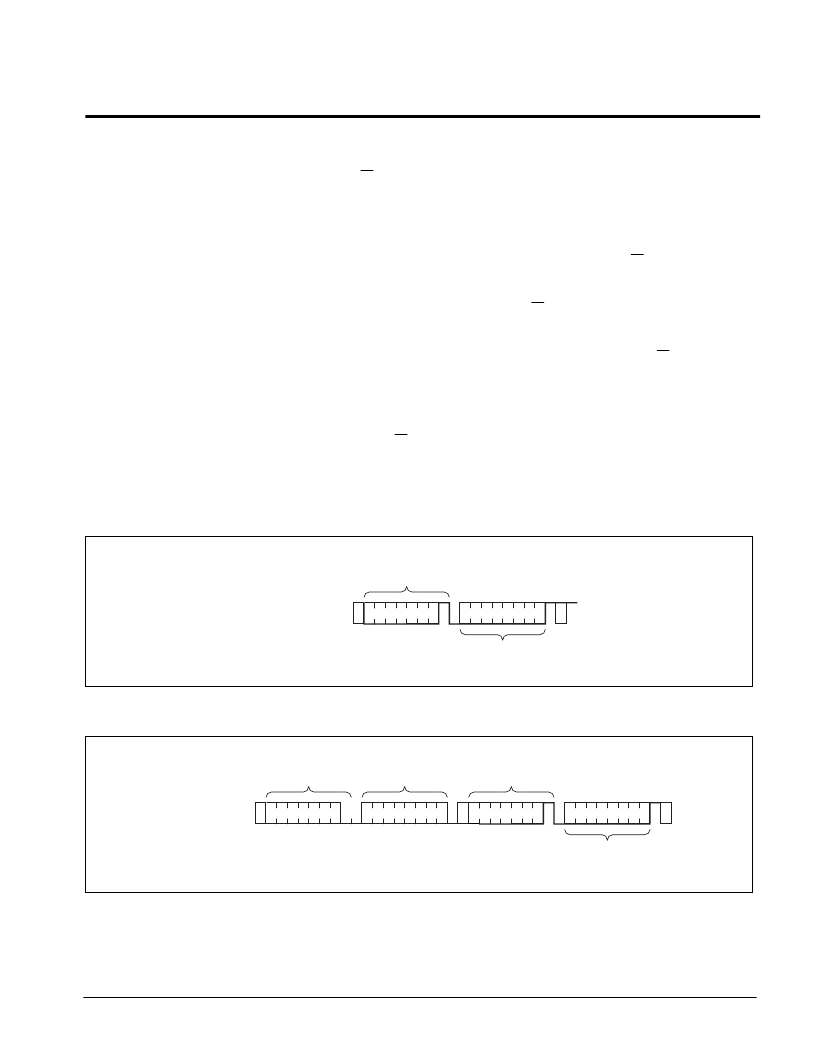

Figure 7. Current Address Read

Figure 8. Random Read

READ OPERATIONS

Read operations are initiated in the same manner as

write operations with the exception that the R/W bit of

the slave address is set HIGH. There are three basic

read operations: current address read, random read

and sequential read.

It should be noted that the ninth clock cycle of the read

operation is not a “don’t care.” To terminate a read op-

eration, the master must either issue a stop condition

during the ninth cycle or hold SDA HIGH during the

ninth clock cycle and then issue a stop condition.

Current Address Read

Internally the X24325 contains an address counter that

maintains the address of the last word read, increment-

ed by one or the exact address of the last word written.

Therefore, if the last access read was to address n, the

next read operation would access data from address

n + 1. Upon receipt of the slave address with the R/W

set HIGH, the X24325 issues an acknowledge and

transmits the eight-bit word. The read operation is ter-

minated by the master; by not responding with an ac-

knowledge and by issuing a stop condition. Refer to

Figure 7 for the sequence of address, acknowledge

and data transfer.

Random Read

Random read operations allow the master to access

any memory location in a random manner. Prior to issu-

ing the slave address with the R/W bit set HIGH, the

master must first perform a “dummy” write operation.

The master issues the start condition, and the slave ad-

dress with the R/W bit set LOW, followed by the word

address it is to read. After the word address acknowl-

edge, the master immediately reissues the start condi-

tion and the slave address with the R/W bit set HIGH.

This will be followed by an acknowledge from the

X24325 and then by the eight-bit word. The read oper-

ation is terminated by the master; by not responding

with an acknowledge and by issuing a stop condition.

Refer to Figure 8 for the address, acknowledge and

data transfer sequence.

BUS ACTIVITY:

MASTER

SDA LINE

BUS ACTIVITY:

X24325

S

T

A

R

T

SLAVE

ADDRESS

S

S

T

O

P

P

A

C

K

DATA

6552 ILL F11

BUS ACTIVITY:

MASTER

SDA LINE

BUS ACTIVITY:

X24325

S

T

A

R

T

SLAVE

ADDRESS

S

A

C

K

6552 ILL F12.1

S

T

A

R

T

S

WORD

ADDRESS n

A

C

K

SLAVE

ADDRESS

DATA n

A

C

K

S

T

O

P

P

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X24325SM | Voltage Regulator IC; Package/Case:5-SOT-23; Supply Voltage Max:15V; Leaded Process Compatible:Yes; Output Voltage Max:15V; Packaging:Cut Tape; Peak Reflow Compatible (260 C):Yes; Number of Channels:4; Source Output Current Max:40mA |

| X24325V | Voltage Regulator IC; Leaded Process Compatible:Yes; Peak Reflow Compatible (260 C):Yes RoHS Compliant: Yes |

| X24325VI | IC STEP-UP SW REG 2A 10-MLPD |

| X24325VM | Advanced 2-Wire Serial E 2 PROM with Block Lock TM Protection |

| X24325V-2.7 | OSC 5V SMT 7X5 CMOS PROGRM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X24325SI-2.7 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Advanced 2-Wire Serial E 2 PROM with Block Lock TM Protection |

| X24325SM | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Advanced 2-Wire Serial E 2 PROM with Block Lock TM Protection |

| X24325SM-2.7 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Advanced 2-Wire Serial E 2 PROM with Block Lock TM Protection |

| X24325V | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Advanced 2-Wire Serial E 2 PROM with Block Lock TM Protection |

| X24325V-2.7 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Advanced 2-Wire Serial E 2 PROM with Block Lock TM Protection |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。