- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371206 > X24C16S14M-3 DVI-D TO VGA ADAPTER PDF資料下載

參數(shù)資料

| 型號: | X24C16S14M-3 |

| 英文描述: | DVI-D TO VGA ADAPTER |

| 中文描述: | 串行E2PROM |

| 文件頁數(shù): | 5/15頁 |

| 文件大?。?/td> | 62K |

| 代理商: | X24C16S14M-3 |

X24C16

5

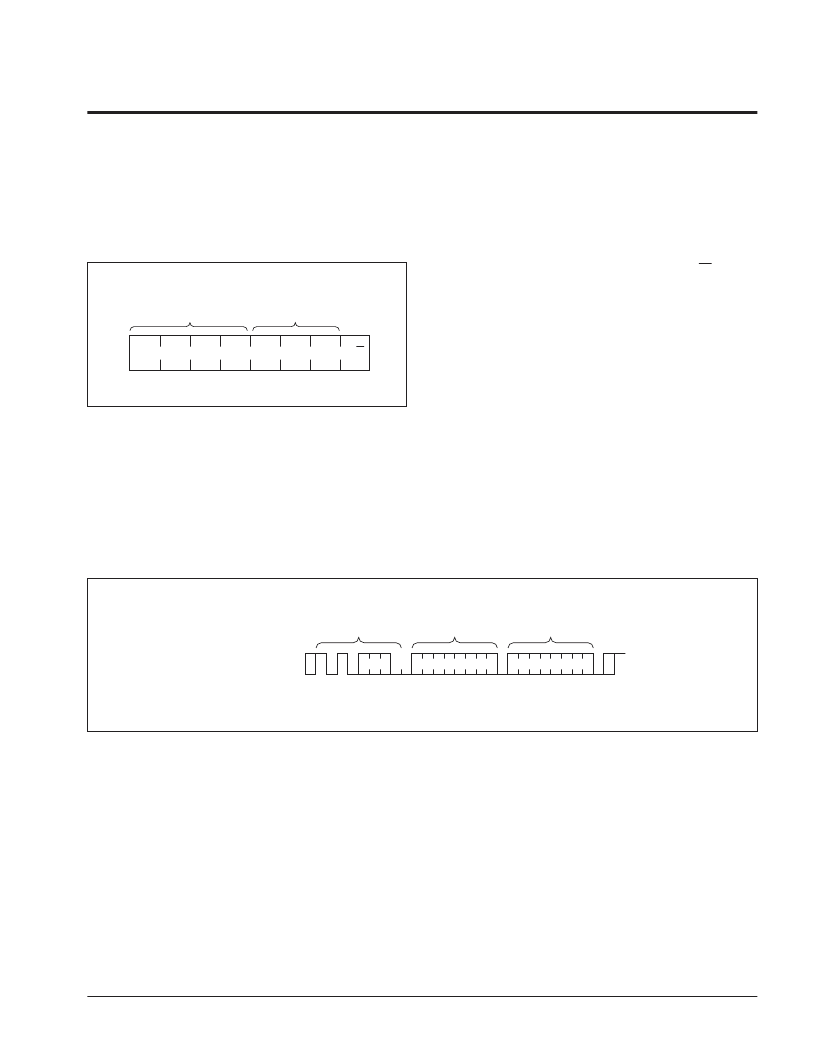

Figure 4. Slave Address

DEVICE ADDRESSING

Following a start condition the master must output the

address of the slave it is accessing. The most significant

four bits of the slave address are the device type identifier

(see Figure 4). For the X24C16 this is fixed as 1010[B].

The next three bits of the slave address field are the bank

select bits. They are used by the host to toggle between

the eight 256 x 8 banks of memory. These are, in effect,

the most significant bits for the word address.

The next three bits of the slave address are an extension

of the array’s address and are concatenated with the

eight bits of address in the word address field, providing

direct access to the whole 2048 x 8 array.

Following the start condition, the X24C16 monitors the

SDA bus comparing the slave address being transmit-

ted with its slave address (device type). Upon a correct

compare the X24C16 outputs an acknowledge on the

SDA line. Depending on the state of the R/W bit, the

X24C16 will execute a read or write operation.

WRITE OPERATIONS

Byte Write

For a write operation, the X24C16 requires a second

address field. This address field is the word address,

comprised of eight bits, providing access to any one of the

2048 words in the array. Upon receipt of the word address

the X24C16 responds with an acknowledge, and awaits

the next eight bits of data, again responding with an

acknowledge. The master then terminates the transfer by

generating a stop condition, at which time the X24C16

begins the internal write cycle to the nonvolatile memory.

While the internal write cycle is in progress the X24C16

inputs are disabled, and the device will not respond to any

requests from the master. Refer to Figure 5 for the

address, acknowledge and data transfer sequence.

3840 FHD F09

Figure 5. Byte Write

BUS ACTIVITY:

MASTER

SDA LINE

BUS ACTIVITY:

X24C16

S

T

A

R

T

SLAVE

ADDRESS

S

S

T

O

P

P

A

C

K

A

C

K

A

C

K

WORD

ADDRESS

DATA

3840 FHD F10

1

0

1

0

A2

A1

A0

R/W

DEVICE TYPE

IDENTIFIER

HIGH

ORDER

WORD

ADDRESS

相關PDF資料 |

PDF描述 |

|---|---|

| X24C16S14M-3.5 | USB TO DVI ADAPTER |

| X24C16PI-2.7 | Serial E2PROM |

| X24C16PI-3 | Serial E2PROM |

| X24C16PI-3.5 | Serial E2PROM |

| X24C16PM-2.7 | Serial E2PROM |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| X24C16S14M-3.5 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Serial E2PROM |

| X24C16S14MB | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Serial E2PROM |

| X24C16S14MB-2.7 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Serial E2PROM |

| X24C16S14MB-3 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Serial E2PROM |

| X24C16S14MB-3.5 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Serial E2PROM |

發(fā)布緊急采購,3分鐘左右您將得到回復。