- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371209 > X24F128PE 2-Wire SerialFlash with Block Lock TM Protection PDF資料下載

參數(shù)資料

| 型號(hào): | X24F128PE |

| 英文描述: | 2-Wire SerialFlash with Block Lock TM Protection |

| 中文描述: | 2線SerialFlash區(qū)塊可鎖定的商標(biāo)保護(hù) |

| 文件頁數(shù): | 7/16頁 |

| 文件大?。?/td> | 80K |

| 代理商: | X24F128PE |

X24F128

7

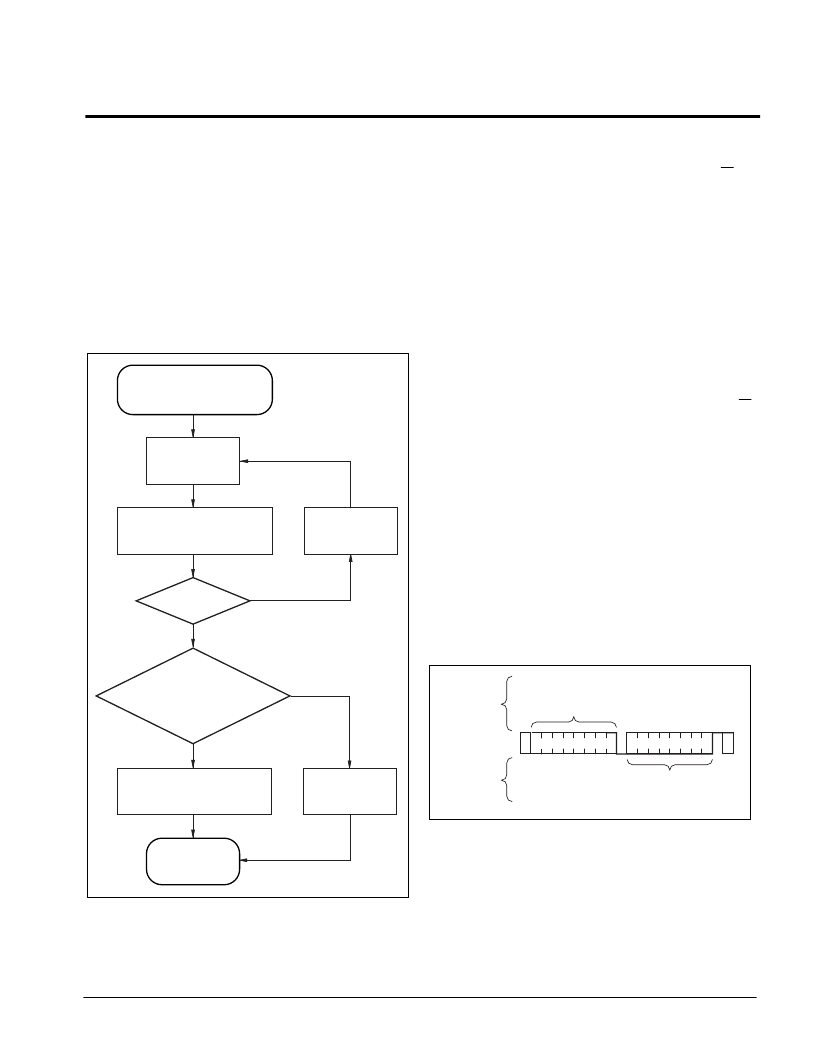

Acknowledge Polling

The maximum program cycle time can be significantly

reduced using Acknowledge Polling. To initiate

Acknowledge Polling, the master issues a start condi-

tion followed by the Slave Address Byte for a program

or read operation. If the device is still busy with the

nonvolatile write cycle, then no ACK will be returned. If

the device has completed the nonvolatile write opera-

tion, an ACK will be returned and the host can then

proceed with the read or program operation. Refer to

figure 6.

7012 ILL F09

BYTE LOAD COMPLETED

BY ISSUING STOP.

ENTER ACK POLLING

ISSUE

START

ISSUE SLAVE

ADDRESS BYTE

(READ OR PROGRAM)

ACK

RETURNED

NONVOLATILE

WRITE

CYCLE COMPLETE.

CONTINUE

SEQUENCE

CONTINUE NORMAL

READ OR PROGRAM

COMMAND SEQUENCE

PROCEED

ISSUE STOP

NO

YES

YES

ISSUE STOP

NO

READ OPERATIONS

Read operations are initiated in the same manner as

program operations with the exception that the R/W bit

of the Slave Address Byte is set to one. There are

three basic read operations: Current Address Reads,

Random Reads, and Sequential Reads.

Current Address Read

Internally, the device contains an address counter that

maintains the address of the last byte read or

programmed, incremented by one. After a read opera-

tion from the last address in the array, the counter will

“roll over” to the first address in the array. After a

program operation to the last address in a given sector,

the counter will “roll over” to the first address of the

same sector.

Upon receipt of the Slave Address Byte with the R/W

bit set to one, the device issues an acknowledge and

then transmits the byte at the current address. The

master terminates the read operation when it does not

respond with an acknowledge during the ninth clock

and then issues a stop condition. Refer to figure 7 for

the address, acknowledge, and data transfer

sequence.

It should be noted that the ninth clock cycle of the read

operation is not a “don’t care.” To terminate a read

operation, the master must either issue a stop condi-

tion during the ninth cycle or hold SDA HIGH during

the ninth clock cycle and then issue a stop condition.

S

T

A

R

T

S

SLAVE

ADDRESS

S

T

O

P

P

A

C

K

DATA

7012 ILL F10

SIGNALS

FROM THE

MASTER

SDA BUS

SIGNALS

FROM THE

SLAVE

1 0 1 0 1

Figure 6. Acknowledge Polling Sequence

Figure 7. Current Address Read Sequence

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X24F128PE-5 | 2-Wire SerialFlash with Block Lock TM Protection |

| X24F128S | 600V 2A 4-PIN SIP .15" LS |

| X24F128SE | 2-Wire SerialFlash with Block Lock TM Protection |

| X24F128S-5 | 2-Wire SerialFlash with Block Lock TM Protection |

| X24F128SE-5 | 2-Wire SerialFlash with Block Lock TM Protection |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X24F128PE-5 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:2-Wire SerialFlash with Block Lock TM Protection |

| X24F128S | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:2-Wire SerialFlash with Block Lock TM Protection |

| X24F128S-5 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:2-Wire SerialFlash with Block Lock TM Protection |

| X24F128SE | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:2-Wire SerialFlash with Block Lock TM Protection |

| X24F128SE-5 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:2-Wire SerialFlash with Block Lock TM Protection |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。