- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371209 > X25020SI SPI Serial E2PROM with Block LockTM Protection PDF資料下載

參數(shù)資料

| 型號: | X25020SI |

| 英文描述: | SPI Serial E2PROM with Block LockTM Protection |

| 中文描述: | SPI串行E2PROM的保護(hù)與塊LockTM |

| 文件頁數(shù): | 1/14頁 |

| 文件大小: | 61K |

| 代理商: | X25020SI |

X25020

1

2K

X25020

256 x 8 Bit

Xicor, Inc. 1994, 1995, 1996 Patents Pending

3834-1.8 6/10/96 T3/C1/D0 NS

Characteristics subject to change without notice

Direct Write

and Block Lock

Protection is a trademark of Xicor, Inc.

SPI Serial E

2

PROM with Block Lock

TM

Protection

3834 FHD F01

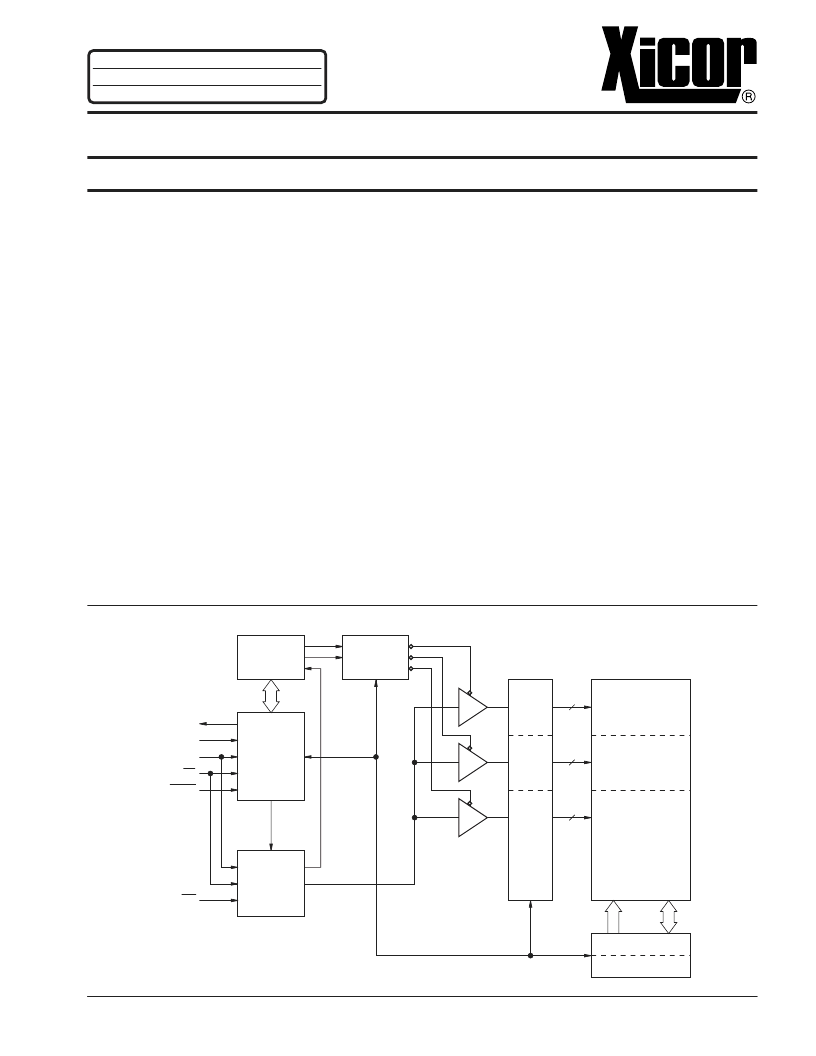

FUNCTIONAL DIAGRAM

A

PPLICATION

N

OTES

A V A I L A B L E

DESCRIPTION

The X25020 is a CMOS 2048-bit serial E

2

PROM, inter-

nally organized as 256 x 8. The X25020 features a serial

interface and software protocol allowing operation on a

simple three-wire bus. The bus signals are a clock input

(SCK) plus separate data in (SI) and data out (SO) lines.

Access to the device is controlled through a chip select

(

CS

) input, allowing any number of devices to share the

same bus.

The X25020 also features two additional inputs that

provide the end user with added flexibility. By asserting

the

HOLD

input, the X25020 will ignore transitions on its

inputs, thus allowing the host to service higher priority

interrupts. The

WP

input can be used as a hardwire input

to the X25020 disabling all write attempts, thus providing

a mechanism for limiting end user capability of altering

the memory.

The X25020 utilizes Xicor’s proprietary Direct Write

cell, providing a minimum endurance of 100,000 cycles

per byte and a minimum data retention of 100 years.

FEATURES

1MHz Clock Rate

SPI Modes (0,0 & 1,1)

256 X 8 Bits

—4 Byte Page Mode

Low Power CMOS

—10

μ

A Standby Current

—3mA Active Write Current

2.7V To 5.5V Power Supply

Block Lock Protection

—Protect 1/4, 1/2 or all of E

2

PROM Array

Built-in Inadvertent Write Protection

—Power-Up/Power-Down protection circuitry

—Write Latch

—Write Protect Pin

Self-Timed Write Cycle

—5ms Write Cycle Time (Typical)

High Reliability

—Endurance: 100,000 cycles per byte

—Data Retention: 100 Years

—ESD protection: 2000V on all pins

8-Lead PDlP Package

8-Lead SOIC Package

COMMAND

DECODE

AND

CONTROL

LOGIC

WRITE

CONTROL

AND

TIMING

LOGIC

WRITE

PROTECT

LOGIC

X DECODE

LOGIC

256 BYTE

ARRAY

16 X 32

Y DECODE

DATA REGISTER

16 X 32

32 X 32

SO

SI

SCK

CS

HOLD

WP

16

16

32

8

4

STATUS

REGISTER

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X25020SI-2.7 | SPI Serial E2PROM with Block LockTM Protection |

| X25020SI-3 | SPI Serial E2PROM with Block LockTM Protection |

| X25040PM-3 | SPI Serial E2PROM with Block LockTM Protection |

| X25040PI | SPI Serial E2PROM with Block LockTM Protection |

| X25040PI-2.7 | SPI Serial E2PROM with Block LockTM Protection |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X25020SI-2.7 | 制造商:ICMIC 制造商全稱:IC MICROSYSTEMS 功能描述:SPI Serial E2PROM with Block LockTM Protection |

| X25020SI-2.7V | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EEPROM |

| X25020SI-3 | 制造商:ICMIC 制造商全稱:IC MICROSYSTEMS 功能描述:SPI Serial E2PROM with Block LockTM Protection |

| X25020SIG-2.7 | 制造商:ICMIC 制造商全稱:IC MICROSYSTEMS 功能描述:SPI Serial E2PROM with Block LockTM Protection |

| X25020SIG-3 | 制造商:ICMIC 制造商全稱:IC MICROSYSTEMS 功能描述:SPI Serial E2PROM with Block LockTM Protection |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。