- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371211 > X25043PI Programmable Watchdog Supervisory E2PROM PDF資料下載

參數(shù)資料

| 型號: | X25043PI |

| 英文描述: | Programmable Watchdog Supervisory E2PROM |

| 中文描述: | 可編程看門狗監(jiān)控E2PROM的 |

| 文件頁數(shù): | 2/15頁 |

| 文件大小: | 93K |

| 代理商: | X25043PI |

X25043/45

2

PIN DESCRIPTIONS

Serial Output (SO)

SO is a push/pull serial data output pin. During a read

cycle, data is shifted out on this pin. Data is clocked out

by the falling edge of the serial clock.

Serial Input (SI)

SI is the serial data input pin. All opcodes, byte ad-

dresses, and data to be written to the memory are input

on this pin. Data is latched by the rising edge of the serial

clock.

Serial Clock (SCK)

The Serial Clock controls the serial bus timing for data

input and output. Opcodes, addresses, or data present

on the SI pin is latched on the rising edge of the clock

input, while data on the SO pin changes after the falling

edge of the clock input.

Chip Select (

CS

)

When

CS

is HIGH, the X25043/45 is deselected and the

SO output pin is at high impedance and, unless an

internal write operation is underway, the X25043/45 will

be in the standby power mode.

CS

LOW enables the

X25043/45, placing it in the active power mode. It should

be noted that after power-up, a HIGH to LOW transition

on

CS

is required prior to the start of any operation.

Write Protect (

WP

)

When

WP

is LOW, nonvolatile writes to the X25043/45

are disabled, but the part otherwise functions normally.

When

WP

is held HIGH, all functions, including nonvola-

tile writes operate normally.

WP

going LOW while

CS

is

still LOW will interrupt a write to the X25043/45. If the

internal write cycle has already been initiated,

WP

going

LOW will have no affect on a write.

Reset (

RESET

, RESET)

X25043/45,

RESET

/RESET is an active LOW/HIGH,

open drain output which goes active whenever V

CC

falls below the mimimum V

CC

sense level. It will remain

active until V

CC

rises above the minimum V

CC

sense

level for 200ms.

RESET

/RESET also goes active if

the Watchdog timer is enabled and

CS

remains either

HIGH or LOW longer than the Watchdog time-out

period. A falling edge of

CS

will reset the watchdog timer.

PIN NAMES

Symbol

CS

SO

SI

SCK

WP

V

SS

V

CC

Description

Chip Select Input

Serial Output

Serial Input

Serial Clock Input

Write Protect Input

Ground

Supply Voltage

Reset Output

RESET

/RESET

3844 PGM T01.1

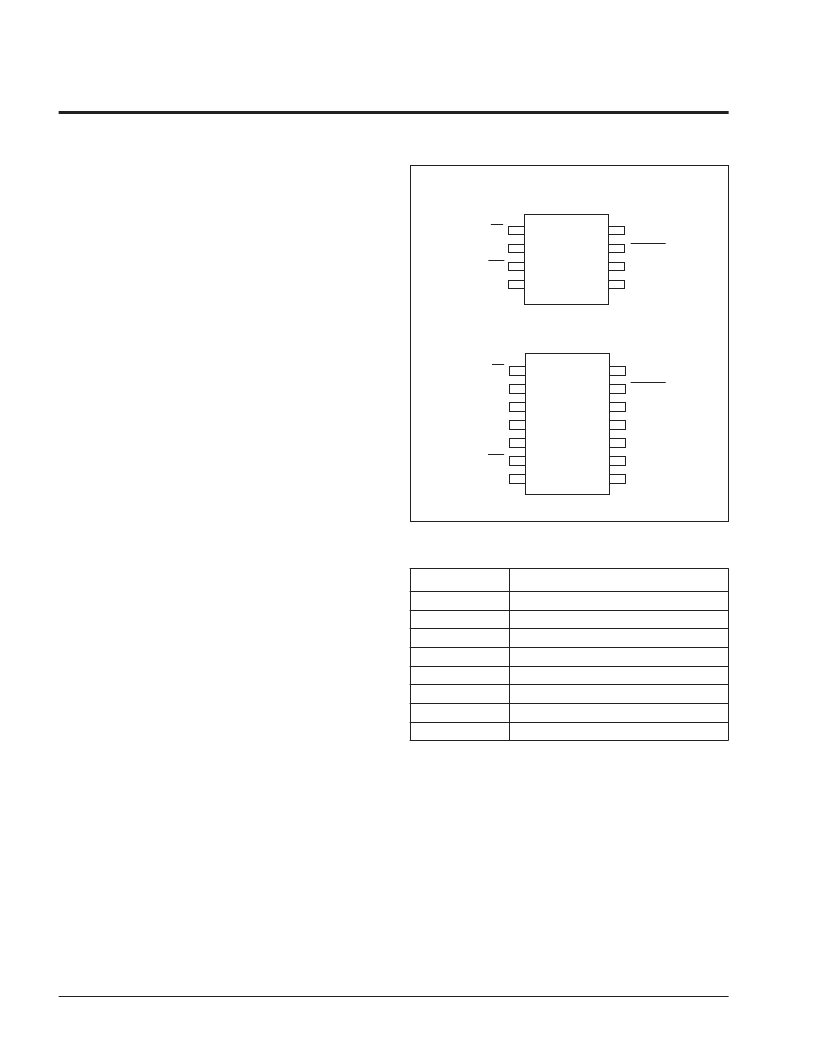

PIN CONFIGURATION

3844 ILL F02.3

CS

SO

WP

VSS

1

2

3

4

8

7

6

5

VCC

RESET/RESET

SCK

SI

8-LEAD DIP/SOIC

X25043/45

14-LEAD TSSOP

X25043/45

CS

SO

NC

NC

NC

WP

VSS

VCC

RESET/RESET

NC

NC

NC

SCK

SI

14

13

12

11

10

9

8

1

2

3

4

5

6

7

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X25043VI | Programmable Watchdog Supervisory E2PROM |

| X25045P-2.7 | Programmable Watchdog Supervisory E2PROM |

| X25045VI | Programmable Watchdog Supervisory E2PROM |

| X25043 | Programmable Watchdog Supervisory E2PROM |

| X25043P | Programmable Watchdog Supervisory E2PROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X25043PI-2.7 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Programmable Watchdog Supervisory E2PROM |

| X25043PI-3 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SPI Serial EEPROM with Supervisory Features |

| X25043S | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Programmable Watchdog Supervisory E2PROM |

| X25043S-2.7 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Programmable Watchdog Supervisory E2PROM |

| X25043S-3 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SPI Serial EEPROM with Supervisory Features |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。