- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371212 > X25080PM-2.7 SPI Serial E2PROM With Block LockTM Protection PDF資料下載

參數(shù)資料

| 型號(hào): | X25080PM-2.7 |

| 英文描述: | SPI Serial E2PROM With Block LockTM Protection |

| 中文描述: | SPI串行E2PROM的保護(hù)帶座LockTM |

| 文件頁(yè)數(shù): | 4/15頁(yè) |

| 文件大小: | 70K |

| 代理商: | X25080PM-2.7 |

第1頁(yè)第2頁(yè)第3頁(yè)當(dāng)前第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)

X25080

4

To read the status register the

CS

line is first pulled LOW

to select the device followed by the 8-bit RDSR instruc-

tion. After the RDSR opcode is sent, the contents of the

status register are shifted out on the SO line. The read

status register sequence is illustrated in Figure 2.

Write Sequence

Prior to any attempt to write data into the X25080, the

“write enable” latch must first be set by issuing the

WREN instruction (See Figure 3).

CS

is first taken LOW,

then the WREN instruction is clocked into the X25080.

After all eight bits of the instruction are transmitted,

CS

must then be taken HIGH. If the user continues the write

operation without taking

CS

HIGH after issuing the

WREN instruction, the write operation will be ignored.

To write data to the E

2

PROM memory array, the user

issues the WRITE instruction, followed by the address

and then the data to be written. This is minimally a thirty-

two clock operation.

CS

must go LOW and remain LOW

for the duration of the operation. The host may continue

to write up to 32 bytes of data to the X25080. The only

restriction is the 32 bytes must reside on the same page.

If the address counter reaches the end of the page and

the clock continues, the counter will “roll over” to the first

address of the page and overwrite any data that may

have been written.

For the write operation (byte or page write) to be

completed,

CS

can only be brought HIGH after bit 0 of

data byte N is clocked in. If it is brought HIGH at any other

time the write operation will not be completed. Refer to

Figures 4 and 5 below for a detailed illustration of the

write sequences and time frames in which

CS

going

HIGH are valid.

To write to the status register, the WRSR instruction is

followed by the data to be written. Data bits 0, 1, 4, 5 and

6 must be “0”. Figure 6 shows this sequence.

While the write is in progress following a status register or

E

2

PROM write sequence, the status register may be read

to check the WIP bit. During this time the WIP bit will be “1”.

Hold Operation

The

HOLD

input should be HIGH (at V

IH

) under normal

operation. If a data transfer is to be interrupted

HOLD

can be pulled LOW to suspend the transfer until it can be

resumed. The only restriction is the SCK input must be

LOW when

HOLD

is first pulled LOW and SCK must also

be LOW when

HOLD

is released.

The

HOLD

input may be tied HIGH either directly to V

CC

or tied to V

CC

through a resistor.

Write-Protect Enable

The Write-Protect-Enable (WPEN) is available for the

X25080 as a nonvolatile enable bit for the

WP

pin.

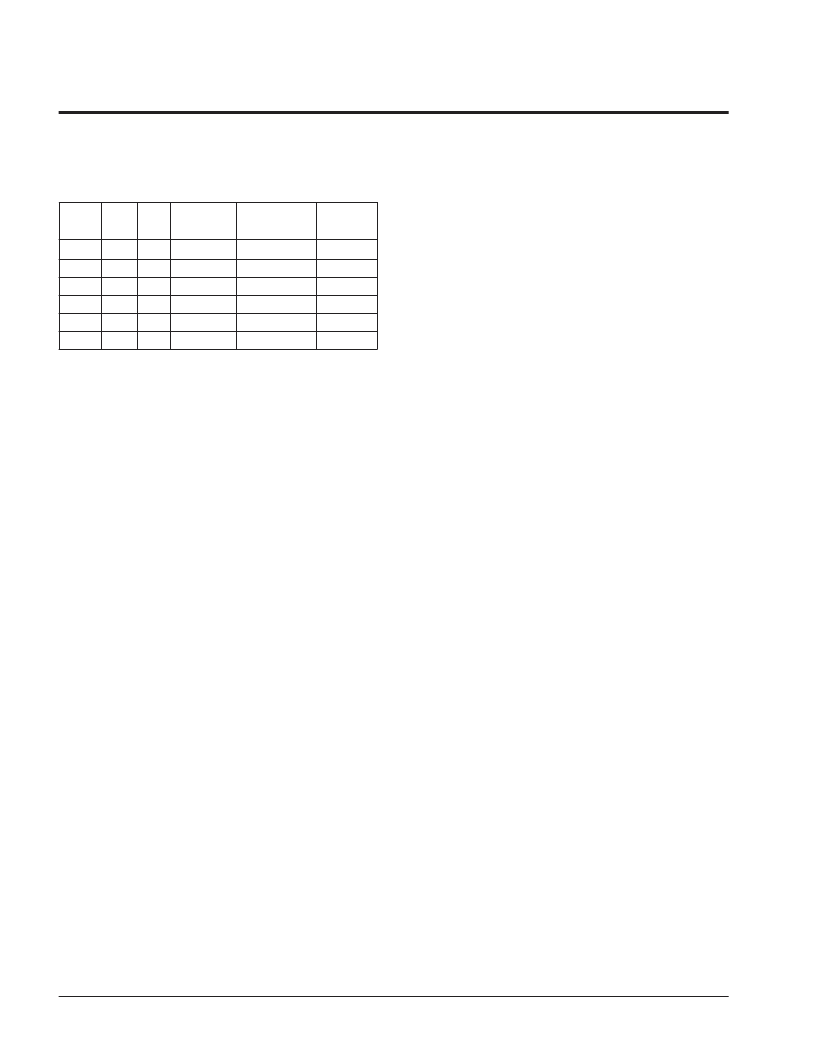

Protected Unprotected

Blocks

Status

Register

WPEN

WP

WEL

Blocks

0

0

1

1

X

X

X

X

0

1

0

1

0

1

Protected

Protected

Protected

Protected

Protected

Protected

Protected

Writable

Protected

Writable

Protected

Writable

Protected

Writable

Protected

Protected

Protected

Writable

3090 PGM T05.1

LOW

LOW

HIGH

HIGH

The Write Protect (

WP

) pin and the nonvolatile Write

Protect Enable (WPEN) bit in the Status Register control

the programmable hardware write protect feature. Hard-

ware write protection is enabled when

WP

pin is LOW,

and the WPEN bit is “1”. Hardware write protection is

disabled when either the

WP

pin is HIGH or the WPEN

bit is “0”. When the chip is hardware write protected,

nonvolatile writes are disabled to the Status Register,

including the Block Protect bits and the WPEN bit itself,

as well as the block-protected sections in the memory

array. Only the sections of the memory array that are not

block-protected can be written.

Note:

Since the WPEN bit is write protected, it

cannot be changed back to a “0”, as long as

the

WP

pin is held LOW.

Clock and Data Timing

Data input on the SI line is latched on the rising edge of

SCK. Data is output on the SO line by the falling edge of

SCK.

Read Sequence

When reading from the E

2

PROM memory array

CS

is

first pulled LOW to select the device. The 8-bit READ

instruction is transmitted to the X25080, followed by the

16-bit address of which the last 10 are used. After the

READ opcode and address are sent, the data stored in

the memory at the selected address is shifted out on the

SO line. The data stored in memory at the next address

can be read sequentially by continuing to provide clock

pulses. The address is automatically incremented to the

next higher address after each byte of data is shifted out.

When the highest address is reached ($03FF) the

address counter rolls over to address $0000 allowing

the read cycle to be continued indefinitely. The read

operation is terminated by taking

CS

HIGH. Refer to the

read E

2

PROM array operation sequence illustrated in

Figure 1.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X25080VI-2.7 | SPI Serial E2PROM With Block LockTM Protection |

| X25080VM-2.7 | SPI Serial E2PROM With Block LockTM Protection |

| X25097M-2.7 | 2-Phase Dual Synchronous PWM Controller with Oscillator Synchronization and Pre-Bias Startup; A IR3621 packaged in a 28-Pin TSSOP on Tape and Reel |

| X25097MI-2.7 | 2-Phase Dual Synchronous PWM Controller with Oscillator Synchronization and Pre-Bias Startup; Similar to IR3621M with Lead-Free packaging. |

| X25097V-1.8 | 5MHz Low Power SPI Serial E 2 PROM with IDLock TM Memory |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X25080S | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:SPI Serial E2PROM With Block LockTM Protection |

| X25080S-2.7 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:SPI Serial E2PROM With Block LockTM Protection |

| X25080SI | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:SPI Serial E2PROM With Block LockTM Protection |

| X25080SI-2.7 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:SPI Serial E2PROM With Block LockTM Protection |

| X25080SM | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:SPI Serial E2PROM With Block LockTM Protection |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。