- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371221 > X25168S8I-1.8 Series 940-F/947, 500 mm to 5000 mm [19.7 in to 196.0 in], Plastic M30, 5 pin M12 x 1, analog output (0 Vdc to 10 Vdc) PDF資料下載

參數(shù)資料

| 型號: | X25168S8I-1.8 |

| 英文描述: | Series 940-F/947, 500 mm to 5000 mm [19.7 in to 196.0 in], Plastic M30, 5 pin M12 x 1, analog output (0 Vdc to 10 Vdc) |

| 中文描述: | V CC的監(jiān)控電路瓦特/ 2 PROM的串行首頁 |

| 文件頁數(shù): | 4/16頁 |

| 文件大?。?/td> | 73K |

| 代理商: | X25168S8I-1.8 |

X25648/49, X25328/29, X25168/69

4

The read only FLAG bit shows the status of a volatile latch

that can be set and reset by the system using the SFLB

and RFLB instructions. The Flag bit is automatically reset

upon power up.

The nonvolatile WPEN bit is programmed using the

WRSR instruction. This bit works in conjunction with the

WP pin to provide Programmable Hardware Write Protec-

tion (Table 2). When WP is LOW and the WPEN bit is pro-

grammed HIGH, all Status Register Write Operations are

disabled.

In Circuit Programmable ROM Mode

This mechanism protects the Block Lock and Watchdog

bits from inadvertant corruption. It may be used to per-

form an In Circuit Programmable ROM function by hard-

wiring the WP pin to ground, writing and Block Locking

the desired portion of the array to be ROM, and then pro-

gramming the WPEN bit HIGH.

Read Sequence

When reading from the E

first pulled low to select the device. The 8-bit READ

instruction is transmitted to the device, followed by the 16-

bit address. After the READ opcode and address are

sent, the data stored in the memory at the selected

address is shifted out on the SO line. The data stored in

memory at the next address can be read sequentially by

continuing to provide clock pulses. The address is auto-

matically incremented to the next higher address after

each byte of data is shifted out. When the highest address

is reached, the address counter rolls over to address

$0000 allowing the read cycle to be continued indefinitely.

The read operation is terminated by taking CS high. Refer

to the Read E

PROM Array Sequence (Figure 1).

2

PROM memory array, CS is

2

To read the Status Register, the CS line is first pulled low

to select the device followed by the 8-bit RDSR instruc-

tion. After the RDSR opcode is sent, the contents of the

Status Register are shifted out on the SO line. Refer to

the Read Status Register Sequence (Figure 2).

Write Sequence

Prior to any attempt to write data into the device, the

“Write Enable” Latch (WEL) must first be set by issuing

the WREN instruction (Figure 3). CS is first taken LOW,

then the WREN instruction is clocked into the device.

After all eight bits of the instruction are transmitted, CS

must then be taken HIGH. If the user continues the Write

Operation without taking CS HIGH after issuing the

WREN instruction, the Write Operation will be ignored.

To write data to the E

issues the WRITE instruction followed by the 16 bit

address and then the data to be written. Any unused bits

are specified to be “0’s”. The WRITE operation minimally

takes 32 clocks. CS must go low and remain low for the

duration of the operation. If the address counter reaches

the end of a page and the clock continues, the counter will

roll back to the first address of the page and overwrite any

data that may have been previously written.

2

PROM memory array, the user then

For the Page Write Operation (byte or page write) to be

completed, CS can only be brought HIGH after bit 0 of the

last data byte to be written is clocked in. If it is brought

HIGH at any other time, the write operation will not be

completed (Figure 4).

To write to the Status Register, the WRSR instruction is

followed by the data to be written (Figure 5). Data bits 0

and 1 must be “0”. Data bits 4 and 5 must be “1”.

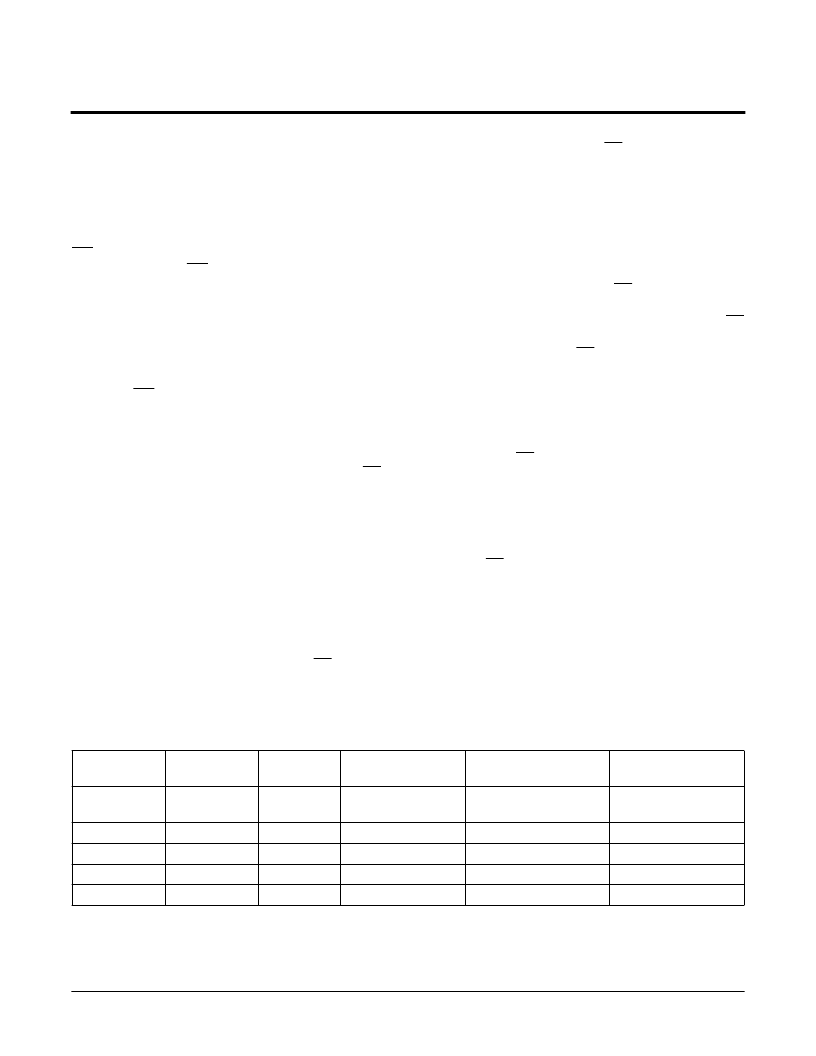

Table 2.

7036 FRM T06

STATUS

REGISTER

STATUS

REGISTER

DEVICE

PIN

BLOCK

PROTECTED

BLOCK

Protected

Protected

Protected

Protected

BLOCK

STATUS

REGISTER

WPEN, BL0,

BL1 BITS

Protected

Protected

Writable

Writable

WEL

0

1

1

1

WPEN

X

1

0

X

WP#

X

0

X

1

UNPROTECTED

BLOCK

Protected

Writable

Writable

Writable

相關PDF資料 |

PDF描述 |

|---|---|

| X25168S14 | V CC Supervisory Circuit w/Serial E 2 PROM |

| X25168S14-1.8 | V CC Supervisory Circuit w/Serial E 2 PROM |

| X25168S14-2.7 | V CC Supervisory Circuit w/Serial E 2 PROM |

| X25168S14I | V CC Supervisory Circuit w/Serial E 2 PROM |

| X25648S8I-2.7 | V CC Supervisory Circuit w/Serial E 2 PROM |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| X25168S8I-2.7 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:V CC Supervisory Circuit w/Serial E 2 PROM |

| X25168V14 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:V CC Supervisory Circuit w/Serial E 2 PROM |

| X25168V14-1.8 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:V CC Supervisory Circuit w/Serial E 2 PROM |

| X25168V14-2.7 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:V CC Supervisory Circuit w/Serial E 2 PROM |

| X25168V14I | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:V CC Supervisory Circuit w/Serial E 2 PROM |

發(fā)布緊急采購,3分鐘左右您將得到回復。