- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371225 > X25F087SI-5 SPI SerialFlash with Block Lock TM Protection PDF資料下載

參數(shù)資料

| 型號(hào): | X25F087SI-5 |

| 英文描述: | SPI SerialFlash with Block Lock TM Protection |

| 中文描述: | 的SPI SerialFlash區(qū)塊可鎖定的商標(biāo)保護(hù) |

| 文件頁(yè)數(shù): | 3/13頁(yè) |

| 文件大小: | 68K |

| 代理商: | X25F087SI-5 |

第1頁(yè)第2頁(yè)當(dāng)前第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)

X25F087

3

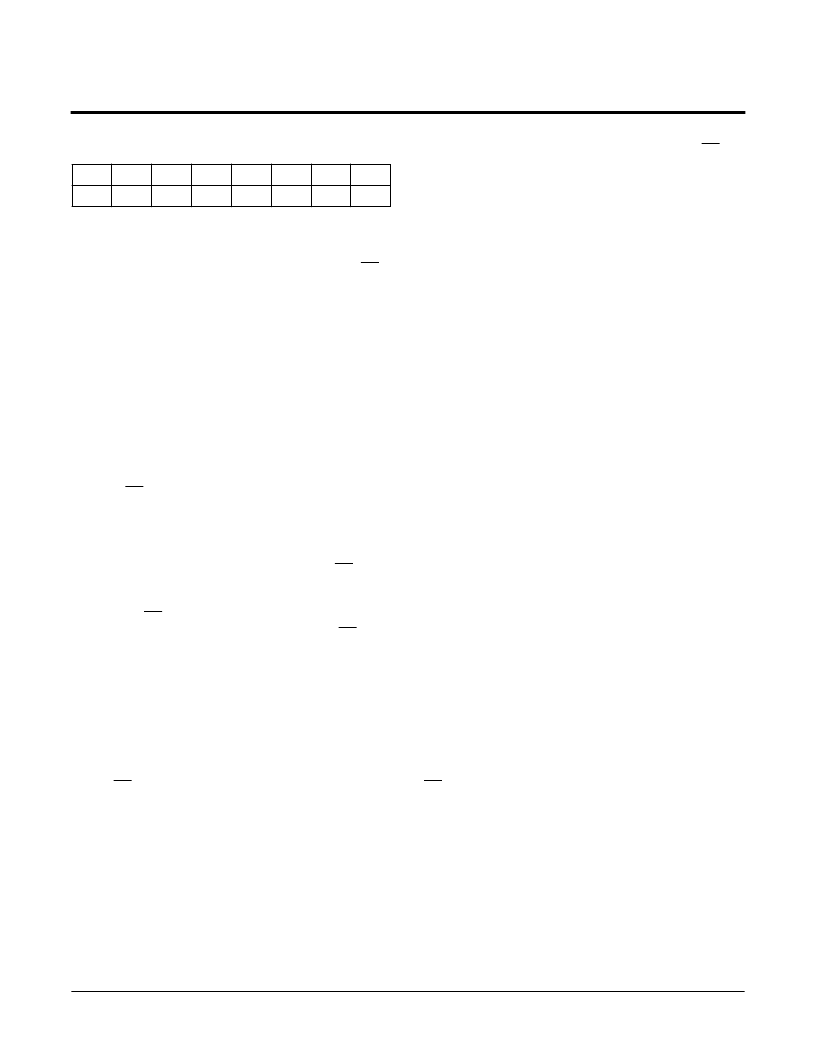

Figure 1. Status Register/Block Lock Protection Byte

Read Sequence

When reading from the SerialFlash memory array, CS is

first pulled LOW to select the device. The 8-bit READ

instruction is transmitted to the X25F087, followed by the

16-bit address, of which the last 10 bits are used (bits

[15:10] specified to be "0’s"). After the READ opcode and

address are sent, the data stored in the memory at the

selected address is shifted out on the SO line. The data

stored in memory at the next address can be read

sequentially by continuing to provide clock pulses. The

address is automatically incremented to the next higher

address after each byte of data is shifted out. When the

highest address is reached (03FFh), the address counter

rolls over to address 0000h, allowing the read cycle to be

continued indefinitely. The read operation is terminated

by taking CS HIGH (Figure 2).

Sector Program Sequence

Prior to any attempt to program data into the X25F087,

the “Program Enable” latch must first be set by issuing

the PREN instruction (Table 1 and Figure 4). CS is first

taken LOW. Then the PREN instruction is clocked into

the X25F087. After all eight bits of the instruction are

transmitted, CS must then be taken HIGH. If the user

continues the program operation without taking CS HIGH

after issuing the PREN instruction, the program opera-

tion will be ignored.

To program data to the SerialFlash memory array, the

user then issues the PROGRAM instruction, followed by

the 16 bit address of the first location in the sector and

then the 16 bytes of data to be programmed. Only the last

9 bits of the address are used and bits [15:9] are speci-

fied to be "0’s". The entire write operation takes 152

clocks. CS must go LOW and remain LOW for the dura-

tion of the operation. The host must program 16 bytes in

each write with the restriction that these bytes reside on

one sector. If the address counter reaches the end of the

sector and the clock continues, or if fewer than 16 bytes

are clocked in, the contents of the sector cannot be guar-

anteed.

For a sector program operation to be completed, CS can

only be brought HIGH after bit 0 of the last data byte to

be programmed is clocked in. If it is brought HIGH at any

other time, the program operation will not be completed.

(Figure 5)

Read Status Operation

If there is not a nonvolatile write in progress, the Read

Status instruction returns the Block Lock Protection byte

from the Status Register which contains the Block Lock

Protection bits BL2-BL0 (Figure 1). The Block Lock Pro-

tection bits define the Block Lock Protection condition

(Figure 1 and Table1). The other bits are reserved and

will return "0’s" when read (Figure 3).

If a nonvolatile write is in progress, the Read Status

instruction returns the status of the internal write opera-

tion on SO. When the nonvolatile write cycle is com-

pleted, the status register data is again read out.

During a nonvolatile write in progress, the SO pin will be

set HIGH. At the end of the nonvolatile write cycle, SO is

set to output the current bit from the status register.

Clocking SCK is valid during a nonvolatile write in

progress, but is not necessary. If the SCK line is clocked,

the pointer to the status register is also clocked, even

though the SO pin shows the status of the nonvolatile

write operation (Figure 3). When the pointer reaches the

end of the eight bit status register, it “rolls over” to the first

bit of the register.

Program Status Operation

Prior to any attempt to perform a Program Status Opera-

tion, the PREN instruction must first be issued. This

instruction sets the “Program Enable” latch and allows

the part to respond to a Program Status sequence (Fig-

ure 6). The Program Status instruction follows and con-

sists of one command byte followed by one Block Lock

Protection byte (Figure 1). This byte contains the Block

Lock Protection bits BL2-BL0. The rest of the bits [7:3]

are unused and must be programmed as “0’s”. Bringing

CS HIGH after the two byte Program Status instruction

initiates a nonvolatile write to the Status Register. Pro-

gramming more than one byte to the Status Register will

overwrite the previously programmed Block Lock Protec-

tion byte (Table 1).

7

0

6

0

5

0

4

0

3

0

2

1

0

BL2

BL1

BL0

Note: Bits [7:3] specified to be “0’s”

7007 FRM T02

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X25F087P-5 | TOUCHSCREEN 10.4 RS-232 |

| X25F087S-5 | RP DPA 60 CONDUCTIVE DUST CAP |

| X25F087V-5 | SPI SerialFlash with Block Lock TM Protection |

| X25F087VI | SPI SerialFlash with Block Lock TM Protection |

| X25F128P-5 | SerialFlash⑩ Memory With Block Lock⑩ Protection |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X25F087V | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:SPI SerialFlash with Block Lock TM Protection |

| X25F087V-5 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:SPI SerialFlash with Block Lock TM Protection |

| X25F087VI | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:SPI SerialFlash with Block Lock TM Protection |

| X25F087VI-5 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:SPI SerialFlash with Block Lock TM Protection |

| X25F128 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:SerialFlash⑩ Memory With Block Lock⑩ Protection |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。