- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371257 > X4285V8I-4.5A (INTERSIL CORP) CPU Supervisor with 128K EEPROM PDF資料下載

參數(shù)資料

| 型號: | X4285V8I-4.5A |

| 廠商: | INTERSIL CORP |

| 元件分類: | 電源管理 |

| 英文描述: | CPU Supervisor with 128K EEPROM |

| 中文描述: | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PDSO8 |

| 封裝: | PLASTIC, TSSOP-8 |

| 文件頁數(shù): | 11/22頁 |

| 文件大小: | 412K |

| 代理商: | X4285V8I-4.5A |

X4283/85 – Preliminary Information

Characteristics subject to change without notice.

11 of 22

REV 1.17 11/27/00

www.xicor.com

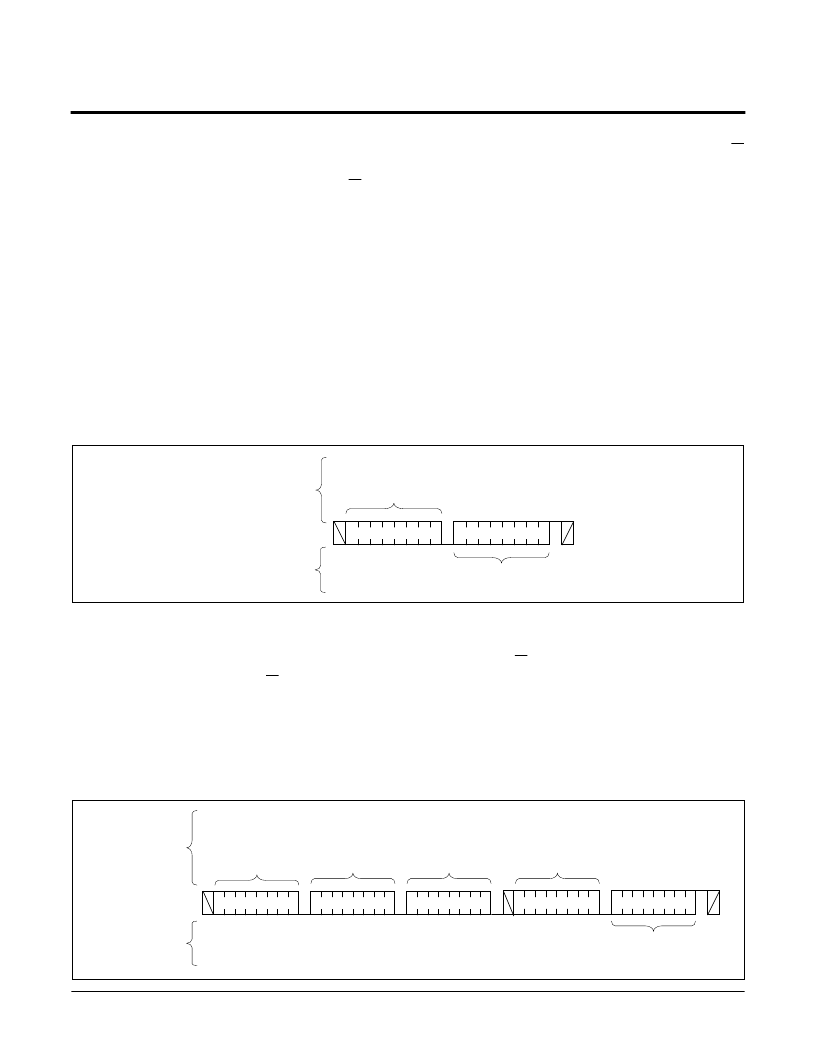

Serial Read Operations

Read operations are initiated in the same manner as

write operations with the exception that the R/W bit of

the Slave Address Byte is set to one. There are three

basic read operations: Current Address Reads, Ran-

dom Reads, and Sequential Reads.

Current Address Read

Internally the device contains an address counter that

maintains the address of the last word read incre-

mented by one. Therefore, if the last read was to

address n, the next read operation would access data

from address n+1. On power up, the address of the

address counter is undefined, requiring a read or write

operation for initialization.

Upon receipt of the Slave Address Byte with the R/W

bit set to one, the device issues an acknowledge and

then transmits the eight bits of the Data Byte. The mas-

ter terminates the read operation when it does not

respond with an acknowledge during the ninth clock

and then issues a stop condition. Refer to Figure 12 for

the

address,

acknowledge,

sequence.

and

data

transfer

It should be noted that the ninth clock cycle of the read

operation is not a “don’t care.” To terminate a read

operation, the master must either issue a stop condi-

tion during the ninth cycle or hold SDA HIGH during the

ninth clock cycle and then issue a stop condition.

Figure 12. Current Address Read Sequence

S

t

a

r

t

S

t

o

p

Slave

Address

Data

A

C

K

SDA Bus

Signals from

the Slave

Signals from

the Master

1

1 0 1 0

Random Read

Random read operation allows the master to access

any memory location in the array. Prior to issuing the

Slave Address Byte with the R/W bit set to one, the

master must first perform a “dummy” write operation.

The master issues the start condition and the Slave

Address Byte, receives an acknowledge, then issues

the Word Address Bytes. After acknowledging receipts

of the Word Address Bytes, the master immediately

issues another start condition and the Slave Address

Byte with the R/W bit set to one. This is followed by an

acknowledge from the device and then by the eight bit

word. The master terminates the read operation by not

responding with an acknowledge and then issuing a

stop condition. Refer to Figure 13 for the address,

acknowledge, and data transfer sequence.

Figure 13. Random Address Read Sequence

0

Slave

Address

Word Address

Byte 1

A

C

K

A

C

K

S

t

a

r

t

S

t

o

p

Slave

Address

Data

A

C

K

1

S

t

a

r

t

SDA Bus

Signals from

the Slave

Signals from

the Master

Word Address

Byte 0

A

C

K

0

1

0

1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X4283 | CPU Supervisor with 128K EEPROM |

| X4283V8I-2.7A | CPU Supervisor with 128K EEPROM |

| X4285V8I-2.7A | CPU Supervisor with 128K EEPROM |

| X4285S8 | CPU Supervisor with 128K EEPROM |

| X4285V8 | CPU Supervisor with 128K EEPROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X-428796A | 制造商:Volex Group 功能描述:LEAD BLACK 2.5M AUSTRALIAN 制造商:Volex Group 功能描述:LEAD, BLACK, 2.5M, AUSTRALIAN |

| X-428802A | 制造商:Volex Group 功能描述:LEAD HOT CONDITION BLACK 2M 制造商:Volex Group 功能描述:LEAD, HOT CONDITION, BLACK, 2M 制造商:Volex Group 功能描述:LEAD, HOT CONDITION, BLACK, 2M; Connector Type A:IEC Socket; Connector Type B:Wire; Voltage Rating:250V; Current Rating:10A; Cable Length - Imperial:6.56ft; Cable Length - Metric:2m; Jacket Colour:Black; SVHC:No SVHC (18-Jun-2012); ;RoHS Compliant: Yes |

| X431 | 制造商:CONNOR-WINFIELD 制造商全稱:Connor-Winfield Corporation 功能描述:3.3V SURFACE MOUNT 5.0 x 7.5mm LVPECL CLOCK OSCILLATOR |

| X431-312.5M | 制造商:CONNOR-WINFIELD 制造商全稱:Connor-Winfield Corporation 功能描述:3.3V SURFACE MOUNT 5.0 x 7.5mm LVPECL CLOCK OSCILLATOR |

| X432-133.33M | 制造商:CONNOR-WINFIELD 制造商全稱:Connor-Winfield Corporation 功能描述:5.0x7.0mm Surface Mount LVCMOS Clock Oscillator Series |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。