- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371268 > X5645S14-2.7 (INTERSIL CORP) RTC Module With CPU Supervisor PDF資料下載

參數(shù)資料

| 型號(hào): | X5645S14-2.7 |

| 廠商: | INTERSIL CORP |

| 元件分類: | 電源管理 |

| 英文描述: | RTC Module With CPU Supervisor |

| 中文描述: | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PDSO14 |

| 封裝: | PLASTIC, SOIC-14 |

| 文件頁數(shù): | 5/19頁 |

| 文件大小: | 117K |

| 代理商: | X5645S14-2.7 |

X5643/X5645

Characteristics subject to change without notice.

5 of 19

REV 1.1.1 3/5/01

www.xicor.com

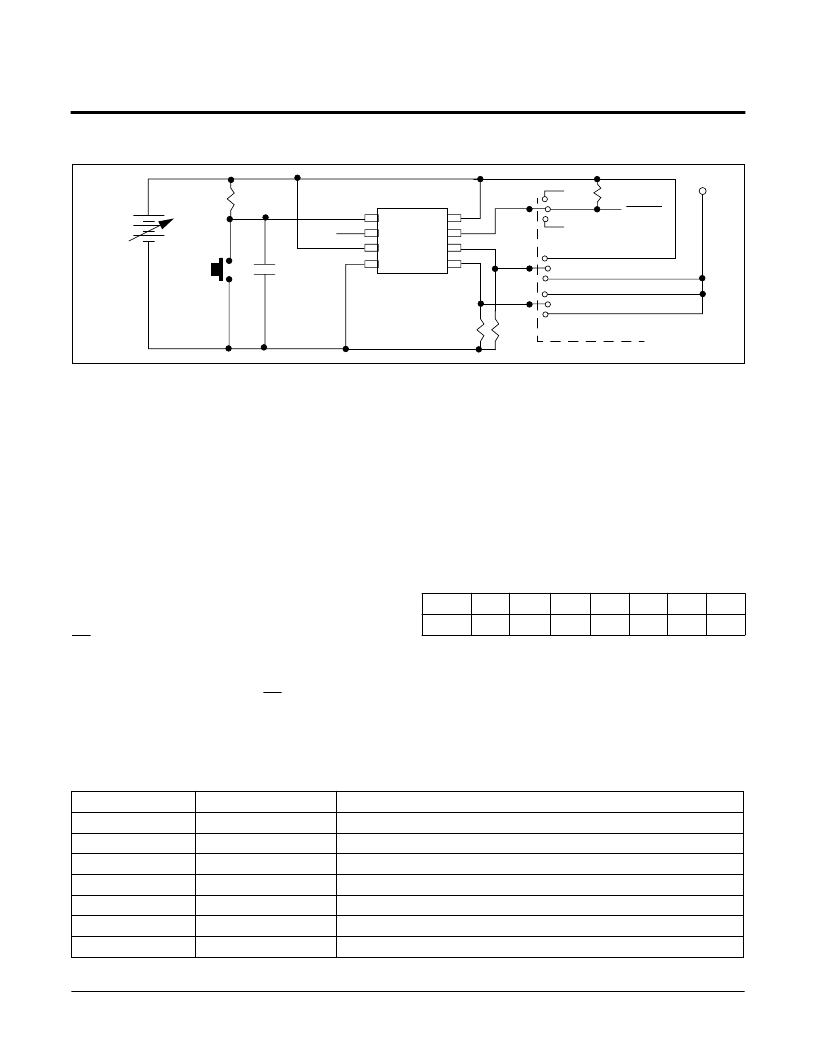

Figure 4. Sample V

TRIP

Reset Circuit

X5643/45

1

2

3

4

8

7

6

5

V

TRIP

Adj.

Program

NC

NC

V

P

Reset V

TRIP

Test

V

TRIP

Set V

TRIP

NC

RESET

4.7K

4.7K

10K

10K

+

SPI SERIAL MEMORY

The memory portion of the device is a CMOS serial

EEPROM array with Xicor’s block lock protection. The

array is internally organized as x 8. The device features

a Serial Peripheral Interface (SPI) and software proto-

col allowing operation on a simple four-wire bus.

The device utilizes Xicor’s proprietary Direct Write

cell, providing a minimum endurance of 100,000 cycles

and a minimum data retention of 100 years.

The device is designed to interface directly with the

synchronous Serial Peripheral Interface (SPI) of many

popular microcontroller families. It contains an 8-bit

instruction register that is accessed via the SI input,

with data being clocked in on the rising edge of SCK.

CS must be LOW during the entire operation.

All instructions (Table 1), addresses and data are trans-

ferred MSB first. Data input on the SI line is latched on

the first rising edge of SCK after CS goes LOW. Data is

output on the SO line by the falling edge of SCK. SCK is

static, allowing the user to stop the clock and then start it

again to resume operations where left off.

Write Enable Latch

The device contains a write enable latch. This latch

must be SET before a write operation is initiated. The

WREN instruction will set the latch and the WRDI

instruction will reset the latch (Figure 3). This latch is

automatically reset upon a power-up condition and

after the completion of a valid Write Cycle.

Status Register

The RDSR instruction provides access to the status regis-

ter. The status register may be read at any time, even dur-

ing a write cycle. The status register is formatted as follows:

The Write-In-Progress (WIP) bit is a volatile, read only

bit and indicates whether the device is busy with an

internal nonvolatile write operation. The WIP bit is read

using the RDSR instruction. When set to a “1”, a non-

volatile write operation is in progress. When set to a

“0”, no write is in progress.

7

6

5

4

3

2

1

0

WPEN

FLB

WD1

WD0

BL1

BL0

WEL

WIP

Table 1. Instruction Set

Note:

*Instructions are shown MSB in leftmost position. Instructions are transferred MSB first.

Instruction Name

WREN

SFLB

WRDI/RFLB

RSDR

WRSR

READ

WRITE

Instruction Format*

0000 0110

0000 0000

0000 0100

0000 0101

0000 0001

0000 0011

0000 0010

Operation

Set the write enable latch (enable write operations)

Set flag bit

Reset the write enable latch/reset flag bit

Read status register

Write status register (watchdog, block lock, WPEN & flag bits)

Read data from memory array beginning at selected address

Write data to memory array beginning at selected address

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X5645S14-2.7A | RTC Module With CPU Supervisor |

| X5645S14I | RTC Module With CPU Supervisor |

| X5645S14I-4.5A | RTC Module With CPU Supervisor |

| X5645 | RTC Module With CPU Supervisor |

| X5645P | RTC Module With CPU Supervisor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X5645S14-4.5A | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:CPU Supervisor with 64Kbit SPI EEPROM |

| X5645S14I | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:CPU Supervisor with 64Kbit SPI EEPROM |

| X5645S14I-2.7 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| X5645S14I-4.5A | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:CPU Supervisor with 64Kbit SPI EEPROM |

| X5645S8-1.8 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SPI Serial EEPROM with Supervisory Features |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。