- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371268 > X5645S14I RTC Module With CPU Supervisor PDF資料下載

參數(shù)資料

| 型號(hào): | X5645S14I |

| 元件分類: | CPU監(jiān)測 |

| 英文描述: | RTC Module With CPU Supervisor |

| 中文描述: | 時(shí)鐘模塊CPU監(jiān)控 |

| 文件頁數(shù): | 6/19頁 |

| 文件大?。?/td> | 117K |

| 代理商: | X5645S14I |

X5643/X5645

Characteristics subject to change without notice.

6 of 19

REV 1.1.1 3/5/01

www.xicor.com

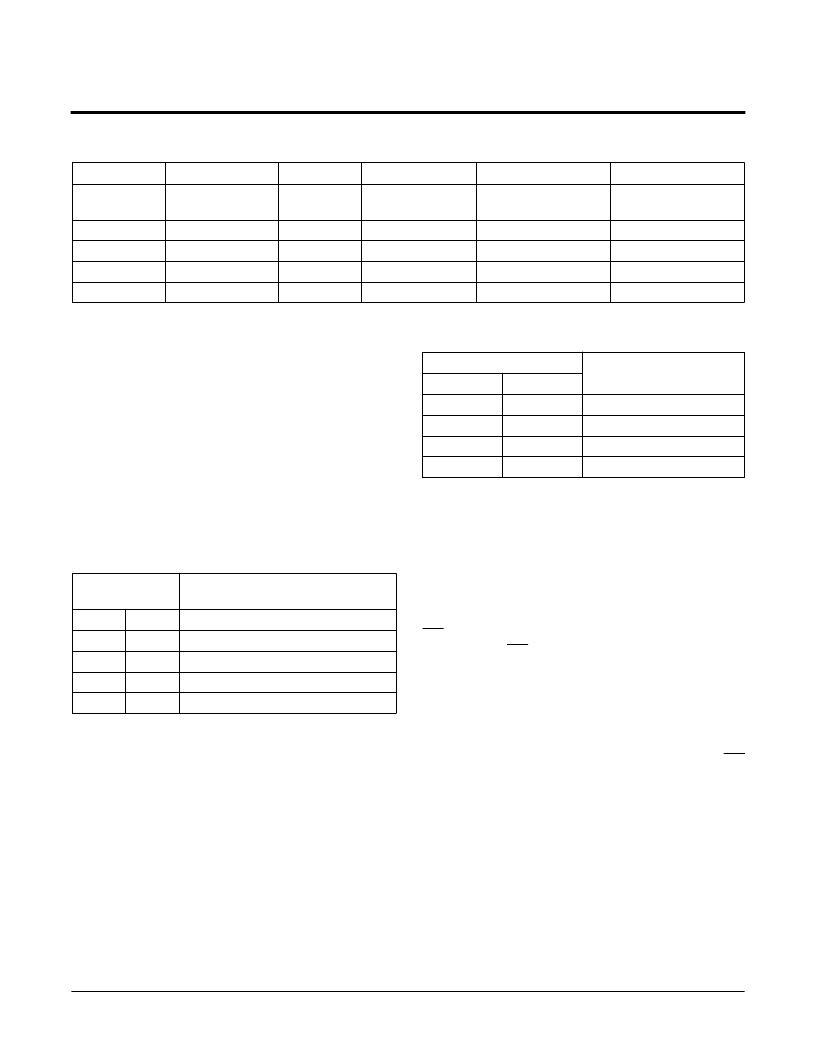

Table 2. Block Protect Matrix

WREN CMD

Status Register

Device Pin

Block

Block

Status Register

WPEN, BL0, BL1

WD0, WD1

Protected

Protected

Writable

Writable

WEL

0

1

1

1

WPEN

X

1

0

X

WP#

X

0

X

1

Protected Block

Protected

Protected

Protected

Protected

Unprotected Block

Protected

Writable

Writable

Writable

The Write Enable Latch (WEL) bit indicates the status

of the write enable latch. When WEL = 1, the latch is

set HIGH and when WEL = 0 the latch is reset LOW.

The WEL bit is a volatile, read only bit. It can be set by

the WREN instruction and can be reset by the WRDS

instruction.

The block lock bits, BL0 and BL1, set the level of block

lock protection. These nonvolatile bits are programmed

using the WRSR instruction and allow the user to pro-

tect one quarter, one half, all or none of the EEPROM

array. Any portion of the array that is block lock pro-

tected can be read but not written. It will remain pro-

tected until the BL bits are altered to disable block lock

protection of that portion of memory.

The watchdog timer bits, WD0 and WD1, select the

watchdog time out period. These nonvolatile bits are

programmed with the WRSR instruction.

The FLAG bit shows the status of a volatile latch that

can be set and reset by the system using the SFLB

and RFLB instructions. The flag bit is automatically

reset upon power up. This flag can be used by the sys-

tem to determine whether a reset occurs as a result of

a watchdog time out or power failure.

The nonvolatile WPEN bit is programmed using the

WRSR instruction. This bit works in conjunction with the

WP pin to provide an in-circuit programmable ROM func-

tion (Table 2). WP is LOW and WPEN bit programmed

HIGH disables all status register write operations.

In Circuit Programmable ROM Mode

This mechanism protects the block lock and watchdog

bits from inadvertent corruption.

In the locked state (

programmable ROM mode) the WP

pin is LOW and the nonvolatile bit WPEN is “1”. This

mode disables nonvolatile writes to the device’s status

register.

Status

Register Bits

BL1

0

0

1

1

Array Addresses Protected

X5643/X5645

None

$1800–$1FFF

$1000–$1FFF

$0000–$1FFF

BL0

0

1

0

1

Status Register Bits

WD1

0

0

1

1

Watchdog Time Out

(Typical)

1.4 seconds

600 milliseconds

200 milliseconds

disabled

WD0

0

1

0

1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X5645S14I-4.5A | RTC Module With CPU Supervisor |

| X5645X14I-4.5A | Analog IC |

| X5645P | RTC Module With CPU Supervisor |

| X5645S14 | RTC Module With CPU Supervisor |

| X5645S14-2.7 | RTC Module With CPU Supervisor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X5645S14I-2.7 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| X5645S14I-4.5A | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:CPU Supervisor with 64Kbit SPI EEPROM |

| X5645S8-1.8 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SPI Serial EEPROM with Supervisory Features |

| X5645S8-2.7 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SPI Serial EEPROM with Supervisory Features |

| X5645X14I-4.5A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。