- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371268 > X68257PI E2 Micro-Peripheral PDF資料下載

參數(shù)資料

| 型號: | X68257PI |

| 英文描述: | E2 Micro-Peripheral |

| 中文描述: | E2微型外設(shè) |

| 文件頁數(shù): | 2/14頁 |

| 文件大?。?/td> | 70K |

| 代理商: | X68257PI |

X68257

2

PIN DESCRIPTIONS

Address/Data (A/D

0

–A/D

7

)

Multiplexed low-order addresses and data. The ad-

dresses flow into the device while AS is HIGH. After AS

transitions from a HIGH to LOW the addresses are

latched. Once the addresses are latched these pins

input data or output data depending on R/

W

,

SEL

, and

CE.

Addresses (A

8

–A

14

)

High order addresses flow into the device when AS = V

IH

and are latched when AS goes LOW.

Chip Enable (

CE

)

The Chip Enable input must be LOW to enable all read/

write operations. When

CE

is HIGH, AS is LOW, and CE

is LOW, the X68257 is placed in the low power standby

mode.

Chip Enable (CE)

Chip Enable is active HIGH. When CE is used to select

the device, the CE must be tied HIGH.

Program Store Enable (

SEL

)

When the X68257 is to be used in a 68XX-based

system,

SEL

is tied to V

SS

.

Read/Write (R/

W

)

When the X68257 is to be used in a 68XX-based

system, R/

W

is tied directly to the microcontroller’s R/

W

output.

Address Strobe (AS)

Addresses flow through the latches to address decoders

when AS is HIGH and are latched when AS transitions

from a HIGH to LOW.

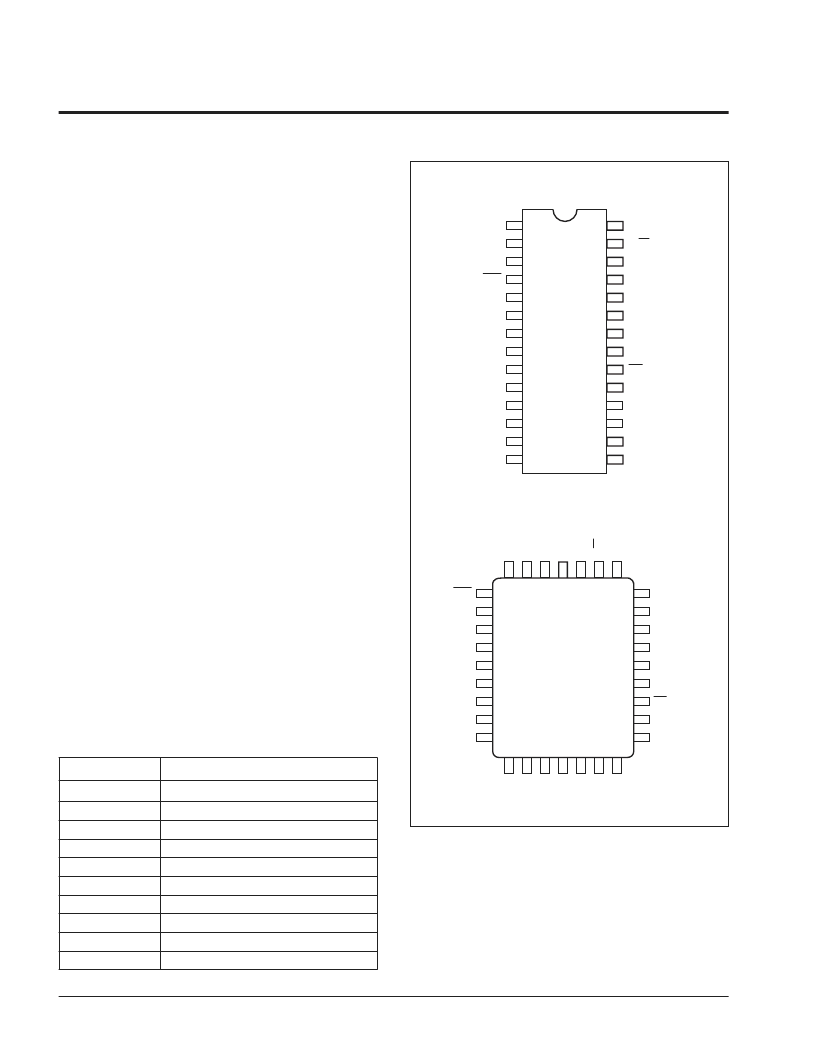

PIN CONFIGURATION

PIN NAMES

Symbol

Description

AS

A/D

0

–A/D

7

A

8

–A

14

E

R/

W

CE,

CE

SEL

V

SS

V

CC

NC

Address Strobe

Address Inputs/Data I/O

Address Inputs

Enable Input

Read/Write Input

Chip Enable

Device Select—Connect to V

SS

Ground

Supply Voltage

No Connect

6539 PGM T01.2

6539 FHD F01.3

A14

A12

AS

SEL

CE

NC

NC

NC

NC

NC

A/D0

A/D1

A/D2

VSS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

VCC

R/W

A13

A8

A9

A11

E

A10

CE

A/D7

A/D6

A/D5

A/D4

A/D3

PDIP

SOIC

X68257

6539 FHD F01A.5

A

SEL

CE

NC

NC

NC

NC

NC

NC

A/D0

A8

A9

A11

NC

E

A10

CE

A/D7

A/D6

A1

A1

VC

R

A1

A1

A2

VS

N

A3

A4

A5

3

2

1 32 31

15 16 17 18 19

5

6

7

8

9

10

11

12

13

28

27

26

25

24

23

22

21

X68257

PLCC

14

20

4

30

29

N

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X68257PM | E2 Micro-Peripheral |

| X68257S | E2 Micro-Peripheral |

| X68257SI | E2 Micro-Peripheral |

| X68257SM | E2 Micro-Peripheral |

| X68C64 | E2 Micro-Peripheral |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X68257PM | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:E2 Micro-Peripheral |

| X68257S | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:E2 Micro-Peripheral |

| X68257SI | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:E2 Micro-Peripheral |

| X68257SM | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:E2 Micro-Peripheral |

| X6855D | 制造商:EPCOS 制造商全稱:EPCOS 功能描述:SAW Components Bandpass Filter |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。