- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371269 > X68C64 E2 Micro-Peripheral PDF資料下載

參數(shù)資料

| 型號(hào): | X68C64 |

| 英文描述: | E2 Micro-Peripheral |

| 中文描述: | E2微型外設(shè) |

| 文件頁(yè)數(shù): | 4/12頁(yè) |

| 文件大?。?/td> | 62K |

| 代理商: | X68C64 |

X68C64

4

MODE SELECTION

CE

E

R/

W

Mode

I/O

Power

V

SS

LOW

HIGH

HIGH

X

X

X

X

Standby

Standby

Read

Write

High Z

High Z

D

OUT

D

IN

Standby (CMOS)

Standby (TTL)

Active

Active

HIGH

HIGH

LOW

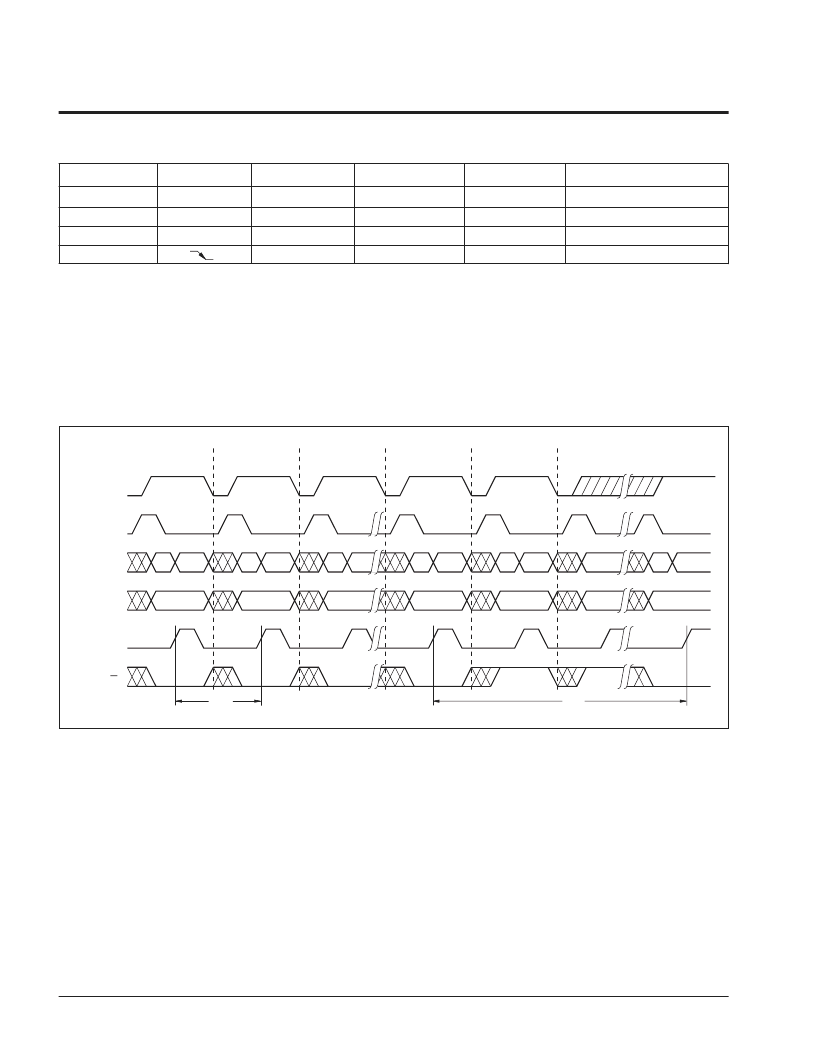

3868 PGM T02.1

requirements. The rising edge of E starts a timer delay-

ing the internal programming cycle 100

μ

s. Therefore,

each successive write operation must begin within 100

μ

s

of the last byte written. The following waveforms illus-

trate the sequence and timing requirements.

PAGE WRITE OPERATION

Regardless of the microcontroller employed, the X68C64

supports page mode write operations. This allows the

microcontroller to write from one to thirty-two bytes of

data to the X68C64. Each individual write within a page

write operation must conform to the byte write timing

Page Write Timing Sequence for E Controlled Operation

Notes:

(1) For each successive write within a page write cycle A

5

–A

12

must be the same.

(2) Although it is not illustrated, the microcontroller may interleave read operations between the individual byte writes within the page

write operation. Two responses are possible.

a. Reading from the same plane being written (A

12

of Read = A

12

of Write) is effectively a Toggle Bit Polling operation.

b. Reading from the opposite plane being written (A

12

of Read

≠

A

12

of Write) true data will be returned, facilitating the use of a

single memory component as both program and data storage.

3868 FHD F07

tBLC

CE

AS

A/D0–A/D7

A8–A12

E

R/W

AIN

DIN

A12=n

OPERATION

BYTE 0

BYTE 1

BYTE 2

LAST BYTE

READ (1)(2)

AFTER tWC READY FOR

NEXT WRITE OPERATION

tWC

AIN

DIN

A12=n

AIN

DIN

A12=n

AIN

DIN

A12=n

AIN

DIN

A12=x

AIN

ADDR

AIN

Next Address

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X68C64P | E2 Micro-Peripheral |

| X68C64PI | E2 Micro-Peripheral |

| X68C64PM | E2 Micro-Peripheral |

| X68C64S | E2 Micro-Peripheral |

| X68C64SI | E2 Micro-Peripheral |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X68C64P | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:E2 Micro-Peripheral |

| X68C64PI | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:E2 Micro-Peripheral |

| X68C64PM | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:E2 Micro-Peripheral |

| X68C64S | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:E2 Micro-Peripheral |

| X68C64SI | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:E2 Micro-Peripheral |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。