- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371277 > X9111 (Intersil Corporation) Single Supply/Low Power/1024-Tap/SPI Bus PDF資料下載

參數(shù)資料

| 型號(hào): | X9111 |

| 廠商: | Intersil Corporation |

| 英文描述: | Single Supply/Low Power/1024-Tap/SPI Bus |

| 中文描述: | 單電源/低Power/1024-Tap/SPI巴士 |

| 文件頁數(shù): | 6/21頁 |

| 文件大?。?/td> | 156K |

| 代理商: | X9111 |

X9111 – Preliminary Information

Characteristics subject to change without notice.

6 of 21

REV 1.1.15 5/9/03

www.xicor.com

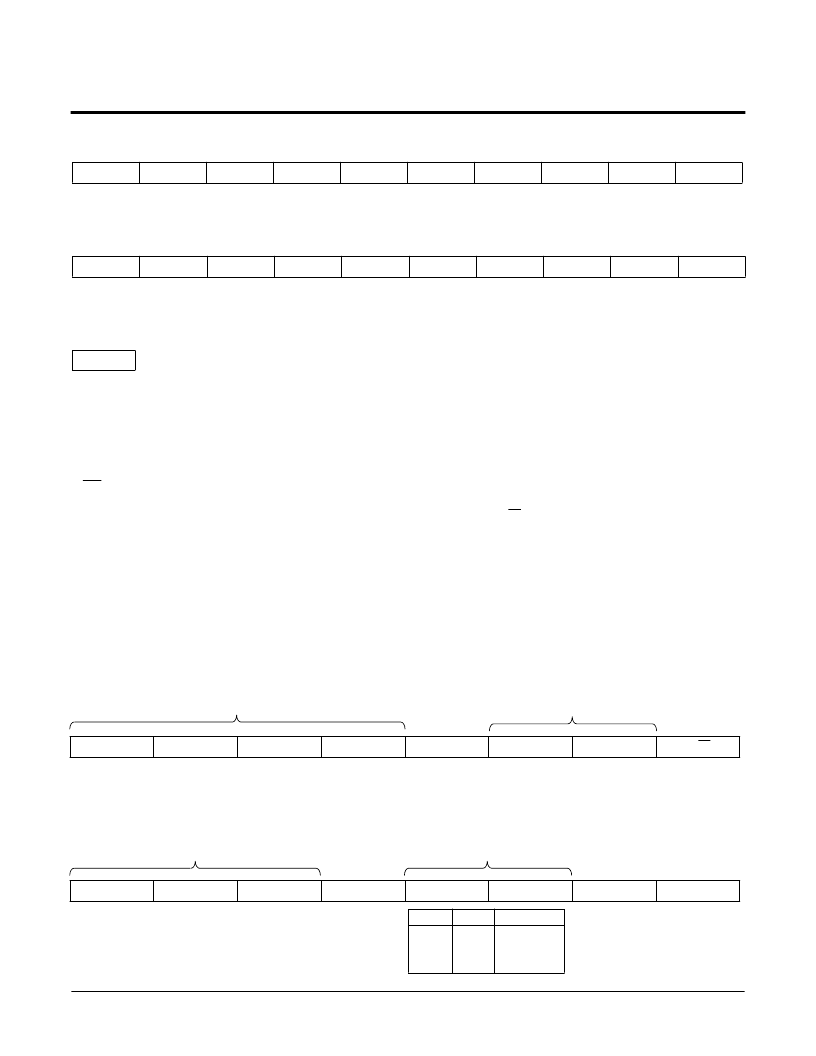

Table 1. Wiper Latch, WL (10-bit), WCR9–WCR0:

Used to store the current wiper position (Volatile, V)

Table 2. Data Register, DR (10-bit), Bit 9–Bit 0:

Used to store wiper positions or data (Non-Volatile, NV)

Table 3. Status Register, SR (1-bit)

WCR9

V

(MSB)

WCR8

V

WCR7

V

WCR6

V

WCR5

V

WCR4

V

WCR3

V

WCR2

V

WCR1

V

WCR0

V

(LSB)

Bit 9

NV

MSB

Bit 8

NV

Bit 7

NV

Bit 6

NV

Bit 5

NV

Bit 4

NV

Bit 3

NV

Bit 2

NV

Bit 1

NV

Bit 0

NV

LSB

WIP

(LSB)

DEVICE INSTRUCTIONS

Identification Byte (ID and A)

The first byte sent to the X9111 from the host, following

a CS going HIGH to LOW, is called the Identification

Byte. The most significant four bits of the slave address

are a device type identifier. The ID[3:0] bits is the

device ID for the X9111; this is fixed as 0101[B] (refer

to Table 4).

The A1–A0 bits in the ID byte are the internal slave

address. The physical device address is defined by the

state of the A1–A0 input pins. The slave address is

externally specified by the user. The X9111 compares

the serial data stream with the address input state; a

successful compare of the address bits is required for

the X9111 to successfully continue the command

sequence. Only the device whose slave address

matches the incoming device address sent by the

master executes the instruction. The A1–A0 inputs can

be actively driven by CMOS input signals or tied to V

CC

or V

SS

. The R/W bit is used to set the device to either

read or write mode.

Instruction Byte and Register Selection

The next byte sent to the X9111 contains the

instruction and register pointer information. The three

most significant bits are used provide the instruction

opcode (I[2:0]). The RB and RA bits point to one of the

four registers. The format is shown in Table 5.

Table 4. Identification Byte Format

Table 5. Instruction Byte Format

Instruction

ID3

0

(MSB)

ID2

1

ID1

0

ID0

1

0

A1

A0

R/W

(LSB)

Device Type

Identifier

Internal Slave

Address

Read or

Write Bit

I2

I1

I0

0

RB

RA

0

0

(MSB)

(LSB)

Opcode

Register

Selection

RB

0

0

1

1

RA

0

1

0

1

Register

DR0

DR1

DR2

DR3

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X9119 | CLAMP |

| X9119TB15 | CLAMP |

| X9119TB15I-2.7 | CLAMP |

| X9119TV14 | Single Supply/Low Power/1024-Tap/2-Wire Bus |

| X9119TV14-2.7 | Single Supply/Low Power/1024-Tap/2-Wire Bus |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X9111_06 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Single Digitally-Controlled (XDCP⑩) Potentiometer |

| X9111TB15 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Single Digitally-Controlled Potentiometer |

| X9111TB15-2.7 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Single Digitally-Controlled Potentiometer |

| X9111TB15I | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Single Digitally-Controlled Potentiometer |

| X9111TB15I-2.7 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Single Digitally-Controlled Potentiometer |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。