- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄9189 > X9258UV24IZ-2.7 (Intersil)IC XDCP QUAD 256TP 50K 24-TSSOP PDF資料下載

參數(shù)資料

| 型號(hào): | X9258UV24IZ-2.7 |

| 廠商: | Intersil |

| 文件頁(yè)數(shù): | 5/19頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC XDCP QUAD 256TP 50K 24-TSSOP |

| 標(biāo)準(zhǔn)包裝: | 62 |

| 系列: | XDCP™ |

| 接片: | 256 |

| 電阻(歐姆): | 50k |

| 電路數(shù): | 4 |

| 溫度系數(shù): | 標(biāo)準(zhǔn)值 ±300 ppm/°C |

| 存儲(chǔ)器類(lèi)型: | 非易失 |

| 接口: | I²C(設(shè)備位址) |

| 電源電壓: | 2.7 V ~ 5.5 V |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類(lèi)型: | 表面貼裝 |

| 封裝/外殼: | 24-TSSOP(0.173",4.40mm 寬) |

| 供應(yīng)商設(shè)備封裝: | 24-TSSOP |

| 包裝: | 管件 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)當(dāng)前第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)

13

FN8168.6

December 15, 2011

Power-Up and Power-Down Requirement

The are no restrictions on the sequencing of the bias supplies

VCC, V+, and V- provided that all three supplies reach their final

values within 1ms of each other. At all times, the voltages on

the potentiometer pins must be less than V+ and more than V-.

The recall of the wiper position from nonvolatile memory is not

in effect until all supplies reach their final value. The VCC ramp

rate specification is always in effect.

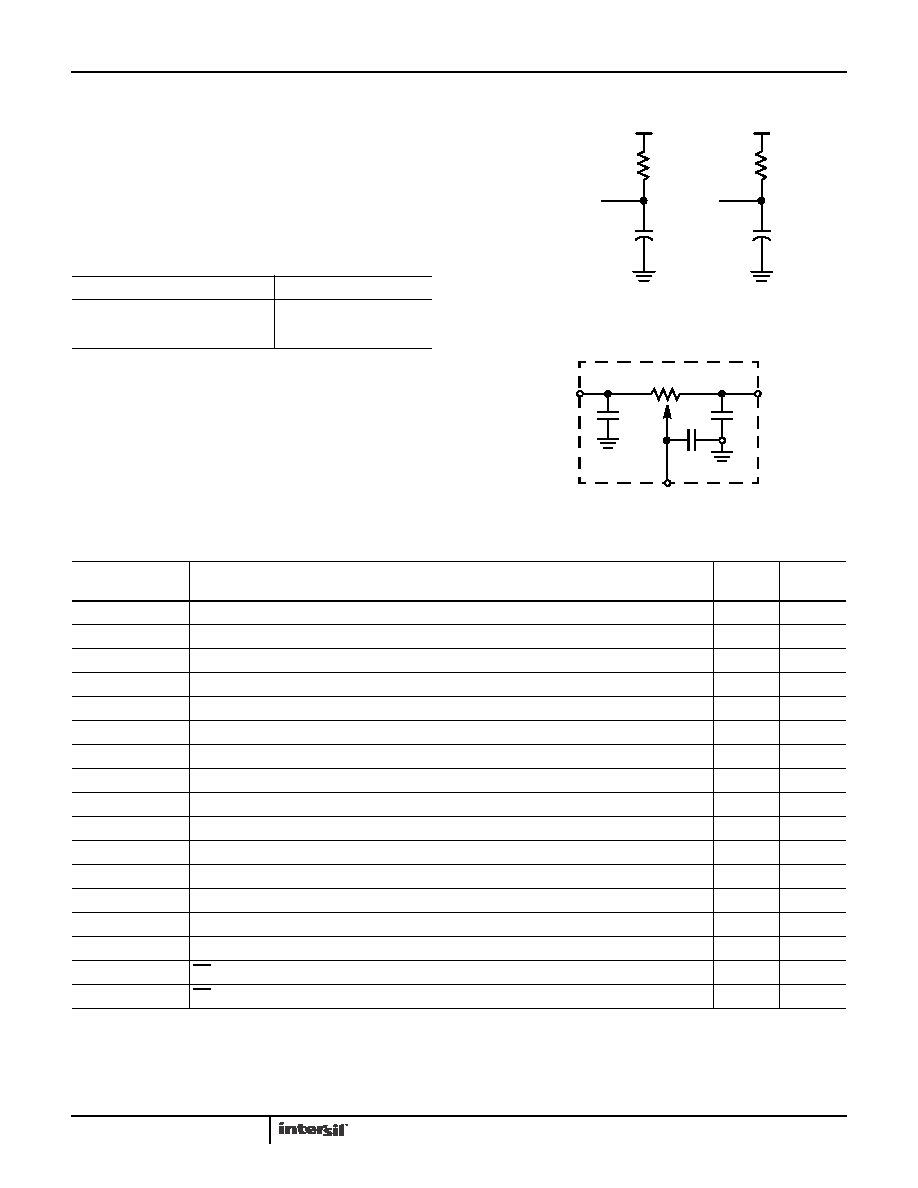

Equivalent AC Load Circuit

Test Circuit #3 SPICE Macro Model

AC Test Conditions

Input Pulse Levels

VCC x 0.1 to VCC x 0.9

Input Rise and Fall Times

10ns

Input and Output Timing Level

VCC x 0.5

5V

1533

100pF

SDA OUTPUT

2.7V

100pF

10pF

RH

RTOTAL

CH

25pF

CW

CL

10pF

RW

RL

MACRO MODEL

AC Timing

Over recommended operating conditions, unless otherwise specified.

SYMBOL

PARAMETER

MIN

(Note 12)

MAX

(Note 12)

UNIT

fSCL

Clock Frequency

400

kHz

tCYC

Clock Cycle Time

2500

ns

tHIGH

Clock High Time

600

ns

tLOW

Clock Low Time

1300

ns

tSU:STA

Start Setup Time

600

ns

tHD:STA

Start Hold Time

600

ns

tSU:STO

Stop Setup Time

600

ns

tSU:DAT

SDA Data Input Setup Time

100

ns

tHD:DAT

SDA Data Input Hold Time

30

ns

tR

SCL and SDA Rise Time (Note 20)

300

ns

tF

SCL and SDA Fall Time (Note 20)

300

ns

tAA

SCL Low to SDA Data Output Valid Time

900

ns

tDH

SDA Data Output Hold Time

50

ns

TI

Noise Suppression Time Constant at SCL and SDA Inputs

50

ns

tBUF

Bus Free Time (Prior to any Transmission)

1300

ns

tSU:WPA

WP, A0, A1, A2 and A3 Setup Time

0

ns

tHD:WPA

WP, A0, A1, A2 and A3 Hold Time

0

ns

NOTE:

20. A device must internally provide a hold time of at least 300ns for the SDA signal in order to bridge the undefined region of the falling edge of SCL.

X9258

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MS3456W20-14SW | CONN PLUG 5POS STRAIGHT W/SCKT |

| X9258TV24IZ-2.7 | IC XDCP QUAD 256TP 100K 24TSSOP |

| MS3456W20-14S | CONN PLUG 5POS STRAIGHT W/SCKT |

| X9258US24IZ-2.7 | IC DGTL POT QUAD 100K 24SOIC |

| MS3456L20-14S | CONN PLUG 5POS STRAIGHT W/SCKT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X9258UV24Z-2.7 | 制造商:INTERSIL 制造商全稱(chēng):Intersil Corporation 功能描述:Quad Digital Controlled Potentiometers |

| X9258UZ24 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:DIGITAL POTENTIOMETER|CMOS|BGA|24PIN|PLASTIC |

| X9258UZ24-2.7 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:DIGITAL POTENTIOMETER|CMOS|BGA|24PIN|PLASTIC |

| X9258UZ24I | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:DIGITAL POTENTIOMETER|CMOS|BGA|24PIN|PLASTIC |

| X9258UZ24I-2.7 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:DIGITAL POTENTIOMETER|CMOS|BGA|24PIN|PLASTIC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。