- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄19825 > XC2C256-7VQG100C (Xilinx Inc)IC CR-II CPLD 256MCELL 100-VQFP PDF資料下載

參數(shù)資料

| 型號(hào): | XC2C256-7VQG100C |

| 廠商: | Xilinx Inc |

| 文件頁(yè)數(shù): | 15/16頁(yè) |

| 文件大小: | 0K |

| 描述: | IC CR-II CPLD 256MCELL 100-VQFP |

| 標(biāo)準(zhǔn)包裝: | 90 |

| 系列: | CoolRunner II |

| 可編程類型: | 系統(tǒng)內(nèi)可編程 |

| 最大延遲時(shí)間 tpd(1): | 6.7ns |

| 電壓電源 - 內(nèi)部: | 1.7 V ~ 1.9 V |

| 邏輯元件/邏輯塊數(shù)目: | 16 |

| 宏單元數(shù): | 256 |

| 門數(shù): | 6000 |

| 輸入/輸出數(shù): | 80 |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 100-TQFP |

| 供應(yīng)商設(shè)備封裝: | 100-VQFP(14x14) |

| 包裝: | 托盤 |

| 產(chǎn)品目錄頁(yè)面: | 601 (CN2011-ZH PDF) |

| 配用: | 122-1573-ND - KIT STARTER COOLRUNNER-II LP/LC 122-1512-ND - KIT DESIGN CPLD W/BATT HOLDER |

| 其它名稱: | 122-1402 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)當(dāng)前第15頁(yè)第16頁(yè)

CoolRunner-II CPLD Family

8

DS090 (v3.1) September 11, 2008

Product Specification

R

nally generated DataGATE control logic can be assigned to

this I/O pin with the BUFG=DATA_GATE attribute.

Global Signals

Global signals, clocks (GCK), sets/resets (GSR), and output

enables (GTS), are designed to strongly resemble each

other. This approach enables design software to make the

best utilization of their capabilities. Each global capability is

supplemented by a corresponding product term version.

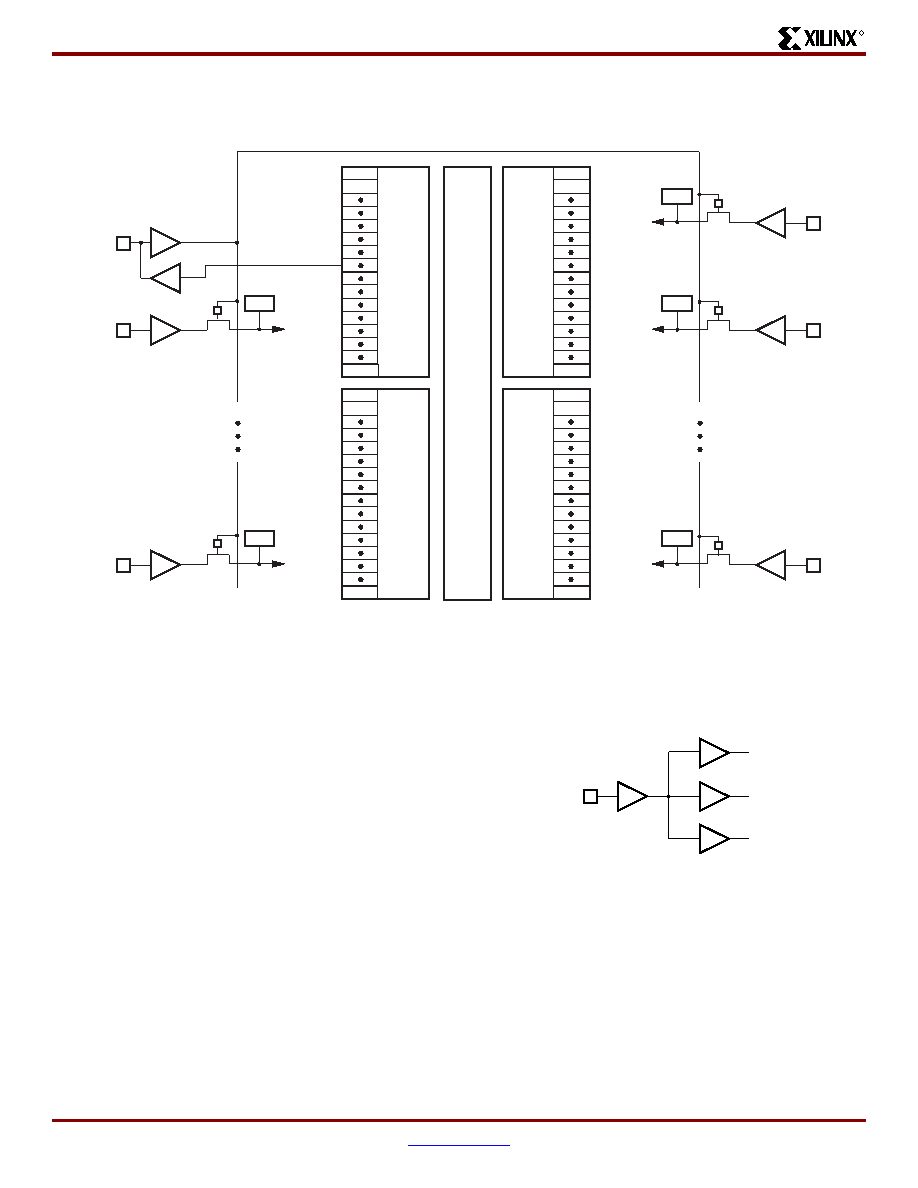

Figure 7 shows the common structure of the global signal

trees. The pin input is buffered, then drives multiple internal

global signal traces to deliver low skew and reduce loading

delays. GCK, GSR, and GTS can also be used as general

purpose I/Os if they are not needed as global signals. The

DataGATE assertion rail is also a global signal.

Figure 6: DataGATE Architecture (output drivers not shown)

PLA

MC1

MC2

MC16

DS090_06_111201

PLA

DataGATE Assertion Rail

PLA

AIM

MC1

MC2

MC16

MC1

MC2

MC16

MC1

MC2

MC16

To AIM

Latch

To AIM

Latch

To AIM

Latch

To AIM

Latch

Figure 7: Global Clocks (GCK), Sets/Resets (GSR), and

Output Enables (GTS)

DS090_07_101001

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ACC35DREH-S13 | CONN EDGECARD 70POS .100 EYELET |

| ISL61851KIBZ | IC USB PWR CTRLR DUAL 8SOIC |

| XC95144XL-7TQG144C | IC CPLD 3.2K 144MCELL 144-TQFP |

| R2D12-0505/P | CONV DC/DC 2W +/-5VOUT SMD |

| VI-BNV-CY-B1 | CONVERTER MOD DC/DC 5.8V 50W |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC2C256-7VQG100I | 功能描述:IC CR-II CPLD 256MCELL 100-VQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - CPLD(復(fù)雜可編程邏輯器件) 系列:CoolRunner II 標(biāo)準(zhǔn)包裝:24 系列:CoolRunner II 可編程類型:系統(tǒng)內(nèi)可編程 最大延遲時(shí)間 tpd(1):7.1ns 電壓電源 - 內(nèi)部:1.7 V ~ 1.9 V 邏輯元件/邏輯塊數(shù)目:24 宏單元數(shù):384 門數(shù):9000 輸入/輸出數(shù):173 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:208-BFQFP 供應(yīng)商設(shè)備封裝:208-PQFP(28x28) 包裝:托盤 |

| XC2C32 | 制造商:XILINX 制造商全稱:XILINX 功能描述:CoolRunner-II CPLD Family |

| XC2C32-6PC44CES | 制造商:Xilinx 功能描述: |

| XC2C32A | 制造商:XILINX 制造商全稱:XILINX 功能描述:CoolRunner-II CPLD Family |

| XC2C32A-4CP56C | 制造商:Xilinx 功能描述:IC SYSTEM GATE 制造商:Xilinx 功能描述:CPLD COOLRUNNER-II 750 GATES 32 MCRCLLS 500MHZ COMM 0.18UM 1 - Trays 制造商:Xilinx 功能描述:IC CPLD 32MC 3.8NS 56BGA 制造商:Xilinx 功能描述:IC CR-II CPLD 32MCELL 56-BGA |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。