- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄21991 > XC2S15-5TQ144C (Xilinx Inc)IC FPGA 2.5V 96 CLB'S 144-PQFP PDF資料下載

參數(shù)資料

| 型號: | XC2S15-5TQ144C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 36/99頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA 2.5V 96 CLB'S 144-PQFP |

| 標(biāo)準(zhǔn)包裝: | 60 |

| 系列: | Spartan®-II |

| LAB/CLB數(shù): | 96 |

| 邏輯元件/單元數(shù): | 432 |

| RAM 位總計: | 16384 |

| 輸入/輸出數(shù): | 86 |

| 門數(shù): | 15000 |

| 電源電壓: | 2.375 V ~ 2.625 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 144-LQFP |

| 供應(yīng)商設(shè)備封裝: | 144-TQFP(20x20) |

| 產(chǎn)品目錄頁面: | 599 (CN2011-ZH PDF) |

| 其它名稱: | 122-1218 XC2S15-5TQ144C-ND |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁當(dāng)前第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁

Spartan-II FPGA Family: Functional Description

DS001-2 (v2.8) June 13, 2008

Module 2 of 4

Product Specification

41

R

IOBUF_<slew_rate>_<drive_strength>

<slew_rate> can be either F (Fast), or S (Slow) and

<drive_strength> is specified in milliamps (2, 4, 6, 8, 12, 16,

or 24).

When the IOBUF primitive supports an I/O standard such

as LVTTL, LVCMOS, or PCI33_5, the IBUF automatically

configures as a 5V tolerant input buffer unless the VCCO for

the bank is less than 2V. If the single-ended IBUF is placed

in a bank with an HSTL standard (VCCO < 2V), the input

buffer is not 5V tolerant.

The voltage reference signal is "banked" within the

Spartan-II device on a half-edge basis such that for all

packages there are eight independent VREF banks

internally. See Figure 36, page 39 for a representation of

the Spartan-II FPGA I/O banks. Within each bank

approximately one of every six I/O pins is automatically

configured as a VREF input.

Additional restrictions on the Versatile I/O IOBUF

placement require that within a given VCCO bank each

IOBUF must share the same output source drive voltage.

Input buffers of any type and output buffers that do not

require VCCO can be placed within the same VCCO bank.

The LOC property can specify a location for the IOBUF.

An optional delay element is associated with the input path

in each IOBUF. When the IOBUF drives an input flip-flop

within the IOB, the delay element activates by default to

ensure a zero hold-time requirement. Override this default

with the NODELAY=TRUE property.

In the case when the IOBUF does not drive an input flip-flop

within the IOB, the delay element de-activates by default to

provide higher performance. To delay the input signal,

activate the delay element with the DELAY=TRUE property.

3-state output buffers and bidirectional buffers can have

either a weak pull-up resistor, a weak pull-down resistor, or

a weak "keeper" circuit. Control this feature by adding the

appropriate primitive to the output net of the IOBUF

(PULLUP, PULLDOWN, or KEEPER).

Versatile I/O Properties

Access to some of the Versatile I/O features (for example,

location constraints, input delay, output drive strength, and

slew rate) is available through properties associated with

these features.

Input Delay Properties

An optional delay element is associated with each IBUF.

When the IBUF drives a flip-flop within the IOB, the delay

element activates by default to ensure a zero hold-time

requirement. Use the NODELAY=TRUE property to

override this default.

In the case when the IBUF does not drive a flip-flop within

the IOB, the delay element by default de-activates to

provide higher performance. To delay the input signal,

activate the delay element with the DELAY=TRUE property.

IOB Flip-Flop/Latch Property

The I/O Block (IOB) includes an optional register on the

input path, an optional register on the output path, and an

optional register on the 3-state control pin. The design

implementation software automatically takes advantage of

these registers when the following option for the Map

program is specified:

map -pr b <filename>

Alternatively, the IOB = TRUE property can be placed on a

register to force the mapper to place the register in an IOB.

Location Constraints

Specify the location of each Versatile I/O primitive with the

location constraint LOC attached to the Versatile I/O

primitive. The external port identifier indicates the value of

the location constrain. The format of the port identifier

depends on the package chosen for the specific design.

The LOC properties use the following form:

LOC=A42

LOC=P37

Output Slew Rate Property

In the case of the LVTTL output buffers (OBUF, OBUFT, and

IOBUF), slew rate control can be programmed with the

SLEW= property. By default, the slew rate for each output

buffer is reduced to minimize power bus transients when

switching non-critical signals. The SLEW= property has one

of the two following values.

SLEW=SLOW

SLEW=FAST

Output Drive Strength Property

For the LVTTL output buffers (OBUF, OBUFT, and IOBUF,

the desired drive strength can be specified with the DRIVE=

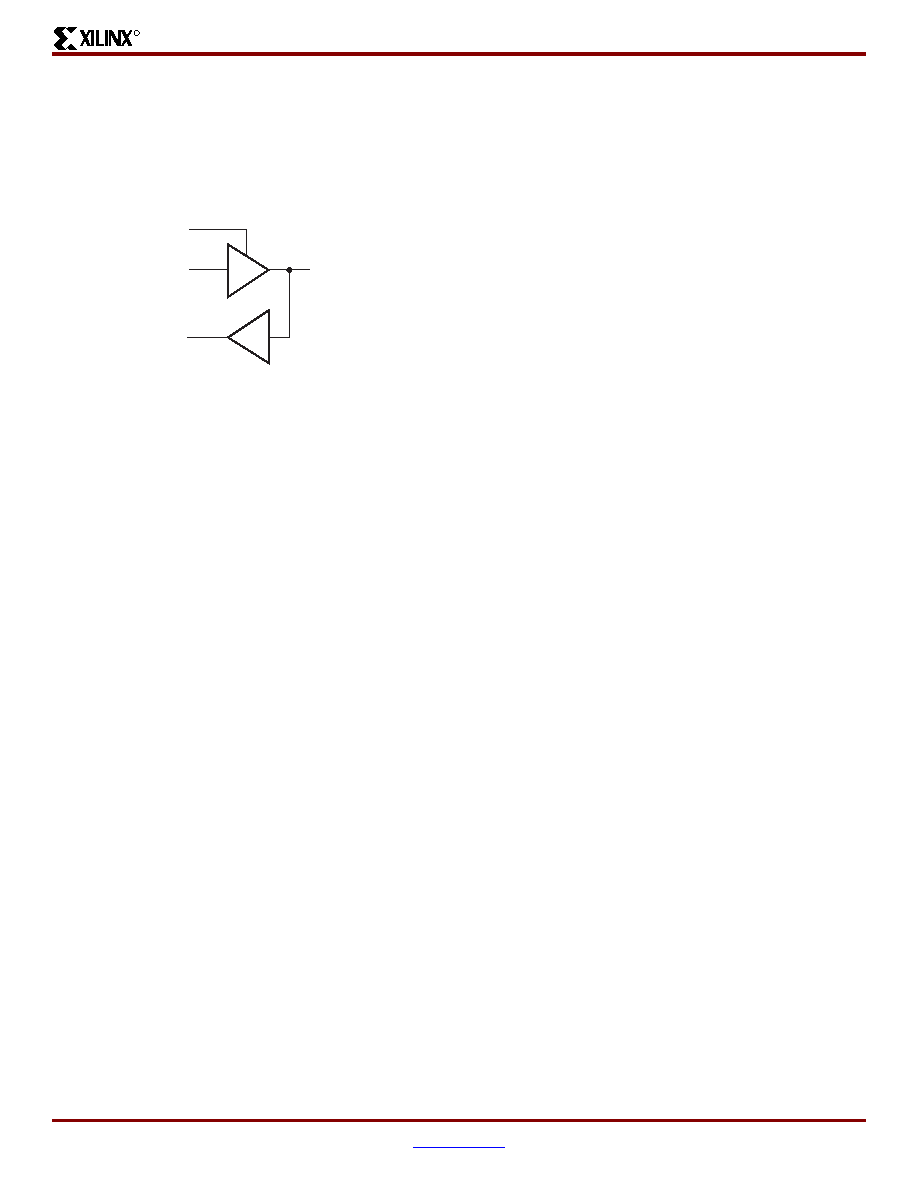

Figure 40: Input/Output Buffer Primitiveprimitive

(IOBUF)

IO

I

IOBUF

DS001_40_061200

T

O

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VE-J6F-CW | CONVERTER MOD DC/DC 72V 100W |

| MAX1617AMEE | IC TEMP SENSOR SMBUS SRL 16-QSOP |

| GBM18DSEI-S243 | CONN EDGECARD 36POS .156 EYELET |

| VE-J60-CW | CONVERTER MOD DC/DC 5V 100W |

| VJ1206A471KBEAT4X | CAP CER 470PF 500V 10% NP0 1206 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC2S15-5TQ144I | 功能描述:IC FPGA 2.5V I-TEMP 144-TQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-II 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計:2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XC2S15-5TQG144C | 制造商:Xilinx 功能描述:FPGA SPARTAN-II 15K GATES 432 CELLS 263MHZ 2.5V 144TQFP EP - Trays 制造商:Xilinx 功能描述:IC SYSTEM GATE 制造商:Xilinx 功能描述:XC2S15-5TQG144C |

| XC2S15-5TQG144I | 制造商:Xilinx 功能描述:IC SYSTEM GATE 制造商:Xilinx 功能描述:FPGA SPARTAN-II 15K GATES 432 CELLS 263MHZ 2.5V 144TQFP EP - Trays |

| XC2S15-5VQ100C | 功能描述:IC FPGA 2.5V 96 CLB'S 100-VQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-II 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計:2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XC2S15-5VQ100I | 功能描述:IC FPGA 2.5V I-TEMP 100-VQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-II 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計:2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。