- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371311 > XC2S400E-6FT256C FPGA PDF資料下載

參數(shù)資料

| 型號(hào): | XC2S400E-6FT256C |

| 英文描述: | FPGA |

| 中文描述: | FPGA的 |

| 文件頁(yè)數(shù): | 7/21頁(yè) |

| 文件大小: | 183K |

| 代理商: | XC2S400E-6FT256C |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)當(dāng)前第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)

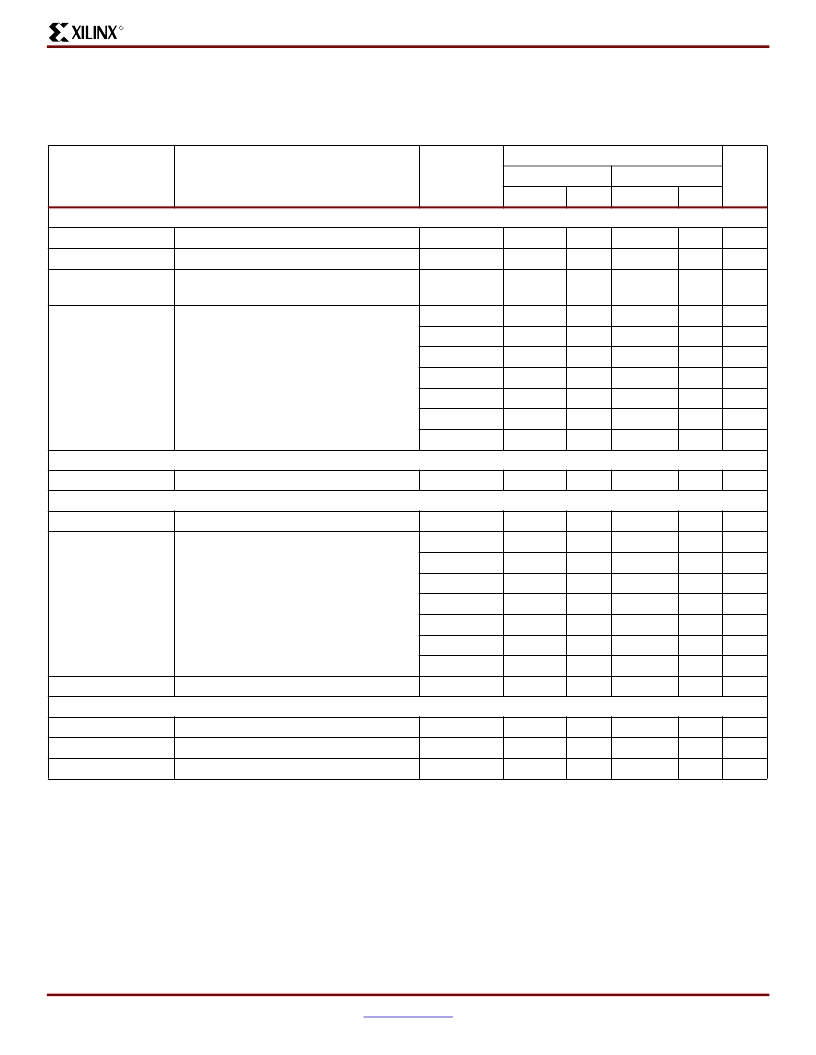

Spartan-IIE 1.8V FPGA Family: DC and Switching Characteristics

DS077-3 (v2.0) November 18, 2002

Product Specification

www.xilinx.com

1-800-255-7778

7

R

IOB Input Switching Characteristics

(1)

Input delays associated with the pad are specified for LVTTL levels. For other standards, adjust the delays with the values

shown in

IOB Input Delay Adjustments for Different Standards

, page 8

.

Symbol

Description

Device

Speed Grade

Units

-7

-6

Min

Max

Min

Max

Propagation Delays

T

IOPI

T

IOPID

T

IOPLI

Pad to I output, no delay

Pad to I output, with delay

Pad to output IQ via transparent latch,

no delay

Pad to output IQ via transparent latch,

with delay

All

All

All

0.4

0.5

0.7

0.8

1.0

1.5

0.4

0.5

0.7

0.8

1.0

1.6

ns

ns

ns

T

IOPLID

XC2S50E

XC2S100E

XC2S150E

XC2S200E

XC2S300E

XC2S400E

XC2S600E

1.3

1.3

1.3

1.3

1.3

1.4

1.5

3.0

3.0

3.2

3.2

3.2

3.2

3.5

1.3

1.3

1.3

1.3

1.3

1.4

1.5

3.1

3.1

3.3

3.3

3.3

3.4

3.7

ns

ns

ns

ns

ns

ns

ns

Sequential Delays

T

IOCKIQ

Setup/Hold Times with Respect to Clock CLK

T

IOPICK

/ T

IOICKP

Pad, no delay

T

IOPICKD

/ T

IOICKPD

Pad, with delay

Clock CLK to output IQ

All

0.1

0.7

0.1

0.7

ns

All

1.4 / 0

2.9 / 0

2.9 / 0

3.1 / 0

3.1 / 0

3.1 / 0

3.2 / 0

3.5 / 0

0.7 / 0.01

-

-

-

-

-

-

-

-

-

1.5 / 0

2.9 / 0

2.9 / 0

3.1 / 0

3.1 / 0

3.1 / 0

3.2 / 0

3.5 / 0

0.7 / 0.01

-

-

-

-

-

-

-

-

-

ns

ns

ns

ns

ns

ns

ns

ns

ns

XC2S50E

XC2S100E

XC2S150E

XC2S200E

XC2S300E

XC2S400E

XC2S600E

All

T

IOICECK

/ T

IOCKICE

ICE input

Set/Reset Delays

T

IOSRCKI

T

IOSRIQ

T

GSRQ

Notes:

1.

Input timing for LVTTL is measured at 1.4V. For other I/O standards, see the table

Delay Measurement Methodology

, page 11

.

SR input (IFF, synchronous)

SR input to IQ (asynchronous)

GSR to output IQ

All

All

All

0.9

0.5

3.8

-

1.0

0.5

3.8

-

ns

ns

ns

1.2

8.5

1.4

9.7

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC2S400E-6FT256I | FPGA |

| XC2S400E-7FG456C | FPGA |

| XC2S400E-7FG676C | FPGA |

| XC2S400E-7FT256C | FPGA |

| XC2S600E-6FG456C | FPGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC2S400E-6FT256I | 制造商:Xilinx 功能描述:FPGA SPARTAN-IIE 400K GATES 10800 CELLS 357MHZ 1.8V 256FTBGA - Trays |

| XC2S400E-6FTG256C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S400E-6FTG256I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S400E-6PQ208C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S400E-6PQ208I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。