- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371311 > XC2S400E-6FT256I FPGA PDF資料下載

參數(shù)資料

| 型號: | XC2S400E-6FT256I |

| 英文描述: | FPGA |

| 中文描述: | FPGA的 |

| 文件頁數(shù): | 3/21頁 |

| 文件大小: | 183K |

| 代理商: | XC2S400E-6FT256I |

Spartan-IIE 1.8V FPGA Family: DC and Switching Characteristics

DS077-3 (v2.0) November 18, 2002

Product Specification

www.xilinx.com

1-800-255-7778

3

R

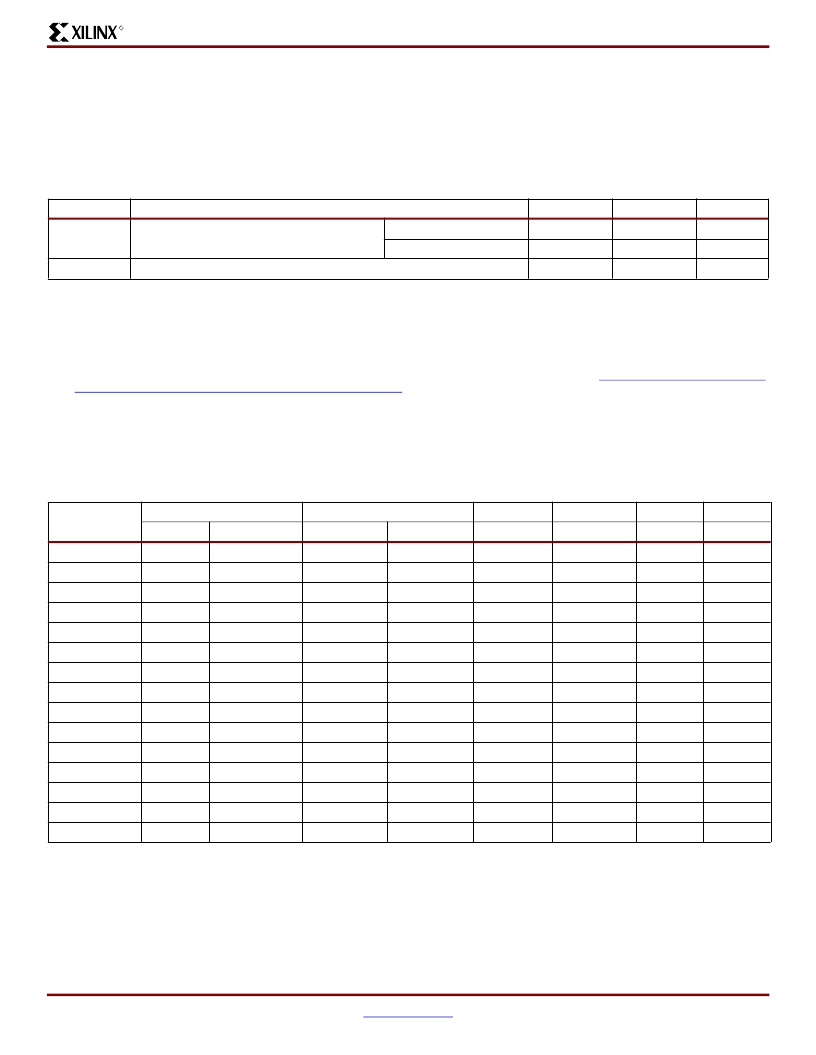

Power-On Requirements

Spartan-IIE FPGAs require that a minimum supply current

I

CCPO

be provided to the V

CCINT

lines for a successful

power-on. If more current is available, the FPGA can con-

sume more than I

CCPO

min., though this cannot adversely

affect reliability.

A maximum limit for I

CCPO

is not specified. Be careful when

using foldback/crowbar supplies and fuses. It is possible to

control the magnitude of I

CCPO

by limiting the supply current

available to the FPGA. A current limit below the trip level will

avoid inadvertently activating over-current protection cir-

cuits.

DC Input and Output Levels

Values for V

IL

and V

IH

are recommended input voltages.

Values for V

OL

and V

OH

are guaranteed output voltages

over the recommended operating conditions. Only selected

standards are tested. These are chosen to ensure that all

standards meet their specifications. The selected standards

are tested at minimum V

CCO

with the respective I

OL

and I

OH

currents shown. Other standards are sample tested.

Symbol

I

CCPO

Description

Min

(1)

500

2

2

Max

-

-

50

Units

mA

A

ms

Total V

CCINT

supply current required

during power-on

Commercial

Industrial

T

CCPO

Notes:

1.

The I

CCPO

requirement applies for a brief time (commonly only a few milliseconds) when V

CCINT

ramps from 0 to 1.8V.

2.

The ramp time is measured from GND to 1.8V on a fully loaded board.

3.

V

CCINT

must not dip in the negative direction during power on.

4.

Power-on current is measured with V

CCINT

and V

CCO

powering up simultaneously.

5.

I/Os are not guaranteed to be disabled until V

CCINT

is applied.

6.

XAPP450 "Power-On Current Requirements for the Spartan-II and Spartan-IIE Families"

.

V

CCINT(2,3)

ramp time

Input/Output

Standard

LVTTL

(1)

LVCMOS2

LVCMOS18

PCI, 3.3V

GTL

GTL+

HSTL I

HSTL III

HSTL IV

SSTL3 I

SSTL3 II

SSTL2 I

SSTL2 II

CTT

AGP

Notes:

1.

V

OL

and V

OH

for lower drive currents are sample tested.

2.

Tested according to the relevant specifications.

V

IL

V

IH

V

OL

V, Max

0.4

0.4

0.4

10% V

CCO

0.4

0.6

0.4

0.4

0.4

V

REF

–

0.6

V

REF

–

0.8

V

REF

–

0.61 V

REF

+ 0.61

V

REF

–

0.8

V

REF

–

0.4

10% V

CCO

V

OH

V, Min

2.4

1.9

V

CCO

–

0.4

90% V

CCO

-

-

V

CCO

–

0.4

V

CCO

–

0.4

V

CCO

–

0.4

V

REF

+ 0.6

V

REF

+ 0.8

I

OL

mA

24

12

8

I

OH

mA

–

24

–

12

–

8

V, Min

–

0.5

–

0.5

–

0.5

–

0.5

–

0.5

–

0.5

–

0.5

–

0.5

–

0.5

–

0.5

–

0.5

–

0.5

–

0.5

–

0.5

–

0.5

V, Max

0.8

0.7

35% V

CCO

30% V

CCO

V

REF

–

0.05

V

REF

–

0.1

V

REF

–

0.1

V

REF

–

0.1

V

REF

–

0.1

V

REF

–

0.2

V

REF

–

0.2

V

REF

–

0.2

V

REF

–

0.2

V

REF

–

0.2

V

REF

–

0.2

V, Min

2.0

1.7

65% V

CCO

50% V

CCO

V

REF

+ 0.05

V

REF

+ 0.1

V

REF

+ 0.1

V

REF

+ 0.1

V

REF

+ 0.1

V

REF

+ 0.2

V

REF

+ 0.2

V

REF

+ 0.2

V

REF

+ 0.2

V

REF

+ 0.2

V

REF

+ 0.2

V, Max

3.6

2.7

1.95

V

CCO

+ 0.5

3.6

3.6

3.6

3.6

3.6

3.6

3.6

3.6

3.6

3.6

3.6

Note (2)

40

36

8

24

48

8

16

7.6

15.2

8

Note (2)

Note (2)

-

-

–

8

–

8

–

8

–

8

–

16

–

7.6

–

15.2

–

8

Note (2)

V

REF

+ 0.8

V

REF

+ 0.4

90% V

CCO

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC2S400E-7FG456C | FPGA |

| XC2S400E-7FG676C | FPGA |

| XC2S400E-7FT256C | FPGA |

| XC2S600E-6FG456C | FPGA |

| XC2S600E-6FG456I | FPGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC2S400E-6FTG256C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S400E-6FTG256I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S400E-6PQ208C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S400E-6PQ208I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S400E-6PQG208C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。