- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371311 > XC2S400E-7FT256C FPGA PDF資料下載

參數(shù)資料

| 型號: | XC2S400E-7FT256C |

| 英文描述: | FPGA |

| 中文描述: | FPGA的 |

| 文件頁數(shù): | 17/21頁 |

| 文件大小: | 183K |

| 代理商: | XC2S400E-7FT256C |

Spartan-IIE 1.8V FPGA Family: DC and Switching Characteristics

DS077-3 (v2.0) November 18, 2002

Product Specification

www.xilinx.com

1-800-255-7778

17

R

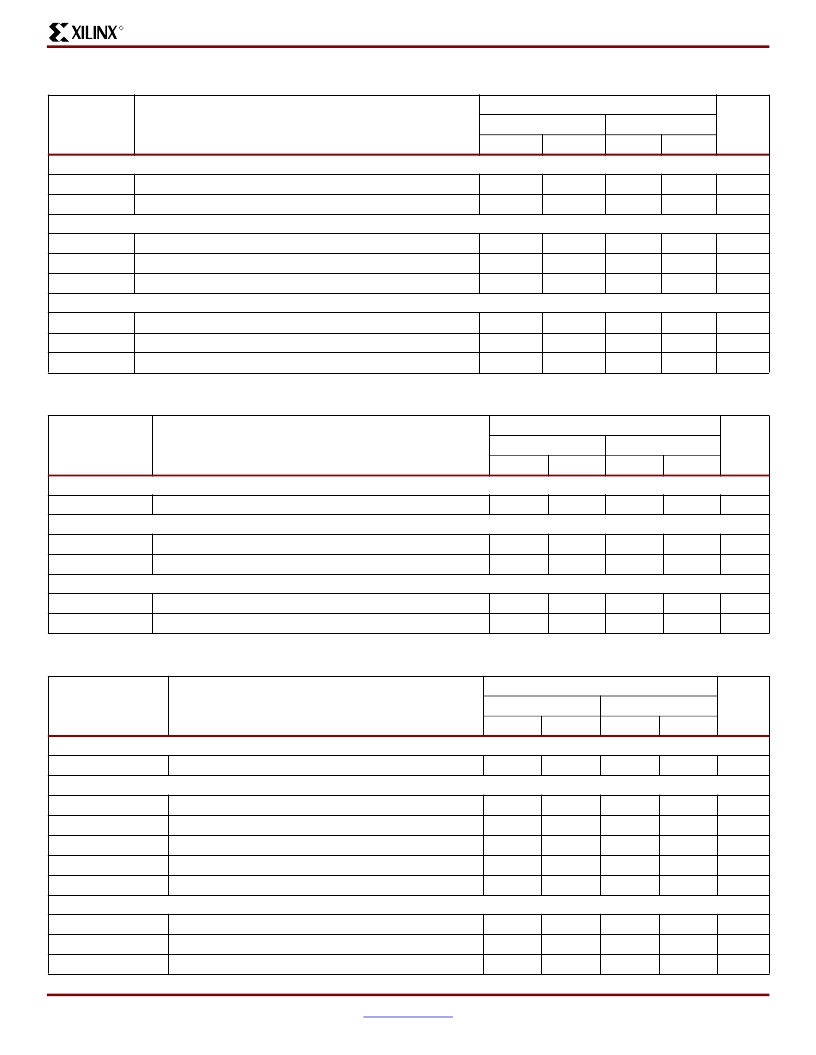

CLB Distributed RAM Switching Characteristics

CLB Shift Register Switching Characteristics

Block RAM Switching Characteristics

Symbol

Sequential Delays

T

SHCKO16

T

SHCKO32

Setup/Hold Times with Respect to Clock CLK

T

AS

/ T

AH

F/G address inputs

T

DS

/ T

DH

BX/BY data inputs (DIN)

T

WS

/ T

WH

CE input (WS)

Clock CLK

T

WPH

Pulse width, High

T

WPL

Pulse width, Low

T

WC

Clock period to meet address write cycle time

Description

Speed Grade

Units

-7

-6

Min

Max

Min

Max

Clock CLK to X/Y outputs (WE active, 16 x 1 mode)

Clock CLK to X/Y outputs (WE active, 32 x 1 mode)

0.6

0.8

1.5

1.9

0.6

0.8

1.7

2.1

ns

ns

0.42 / 0

0.53 / 0

0.7 / 0

-

-

-

0.5 / 0

0.6 / 0

0.8 / 0

-

-

-

ns

ns

ns

2.1

2.1

4.2

-

-

-

2.4

2.4

4.8

-

-

-

ns

ns

ns

Symbol

Sequential Delays

T

REG

Setup/Hold Times with Respect to Clock CLK

T

SHDICK

BX/BY data inputs (DIN)

T

SHCECK

CE input (WS)

Clock CLK

T

SRPH

Pulse width, High

T

SRPL

Pulse width, Low

Description

Speed Grade

Units

-7

-6

Min

Max

Min

Max

Clock CLK to X/Y outputs

1.2

2.9

1.2

3.2

ns

0.53 / 0

0.7 / 0

-

-

0.6 / 0

0.8 / 0

-

-

ns

ns

2.1

2.1

-

-

2.4

2.4

-

-

ns

ns

Symbol

Description

Speed Grade

Units

-7

-6

Min

Max

Min

Max

Sequential Delays

T

BCKO

Setup/Hold Times with Respect to Clock CLK

T

BACK

/ T

BCKA

ADDR inputs

T

BDCK

/ T

BCKD

DIN inputs

T

BECK

/ T

BCKE

EN inputs

T

BRCK

/ T

BCKR

RST input

T

BWCK

/ T

BCKW

WEN input

Clock CLK

T

BPWH

Pulse width, High

T

BPWL

Pulse width, Low

T

BCCS

CLKA -> CLKB setup time for different ports

Clock CLK to DOUT output

0.6

3.1

0.6

3.5

ns

1.0 / 0

1.0 / 0

2.2 / 0

2.1 / 0

2.0 / 0

-

-

-

-

-

1.1 / 0

1.1 / 0

2.5 / 0

2.3 / 0

2.2 / 0

-

-

-

-

-

ns

ns

ns

ns

ns

1.4

1.4

2.7

-

-

-

1.5

1.5

3.0

-

-

-

ns

ns

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC2S600E-6FG456C | FPGA |

| XC2S600E-6FG456I | FPGA |

| XC2S600E-6FG676C | FPGA |

| XC2S600E-6FG676I | FPGA |

| XC2S600E-7FG456C | FPGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC2S400E-7FT256I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S400E-7FTG256C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S400E-7FTG256I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S400E-7PQ208C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S400E-7PQ208I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。