- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4296 > XC2S50-5TQ144C (Xilinx Inc)IC FPGA 2.5V 384 CLB'S 144-TQFP PDF資料下載

參數(shù)資料

| 型號(hào): | XC2S50-5TQ144C |

| 廠商: | Xilinx Inc |

| 文件頁(yè)數(shù): | 99/99頁(yè) |

| 文件大小: | 0K |

| 描述: | IC FPGA 2.5V 384 CLB'S 144-TQFP |

| 標(biāo)準(zhǔn)包裝: | 60 |

| 系列: | Spartan®-II |

| LAB/CLB數(shù): | 384 |

| 邏輯元件/單元數(shù): | 1728 |

| RAM 位總計(jì): | 32768 |

| 輸入/輸出數(shù): | 92 |

| 門數(shù): | 50000 |

| 電源電壓: | 2.375 V ~ 2.625 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 144-LQFP |

| 供應(yīng)商設(shè)備封裝: | 144-TQFP(20x20) |

| 其它名稱: | 122-1225 XC2S50-5TQ144C-ND |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)當(dāng)前第99頁(yè)

Spartan-II FPGA Family: Pinout Tables

DS001-4 (v2.8) June 13, 2008

Module 4 of 4

Product Specification

99

R

Revision History

11/02/00

FG456

VCCINT Pins

E5

E18

F6

F17

G7

G8

G9

G14

G15

G16

H7

H16

J7

J16

P7

P16

R7

R16

T7

T8

T9

T14

T15

T16

U6

U17

V5

V18

-

VCCO Bank 0 Pins

F7

F8

F9

F10

G10

G11

VCCO Bank 1 Pins

F13

F14

F15

F16

G12

G13

VCCO Bank 2 Pins

G17

H17

J17

K16

K17

L16

VCCO Bank 3 Pins

M16

N16

N17

P17

R17

T17

VCCO Bank 4 Pins

T12

T13

U13

U14

U15

U16

VCCO Bank 5 Pins

T10

T11

U7

U8

U9

U10

VCCO Bank 6 Pins

M7

N6

N7

P6

R6

T6

VCCO Bank 7 Pins

Additional XC2S200 Package Pins (Continued)

G6

H6

J6

K6

K7

L7

GND Pins

A1

A22

B2

B21

C3

C20

J9

J10

J11

J12

J13

J14

K9

K10

K11

K12

K13

K14

L9

L10

L11

L12

L13

L14

M9

M10

M11

M12

M13

M14

N9

N10

N11

N12

N13

N14

P9

P10

P11

P12

P13

P14

Y3

Y20

AA2

AA21

AB1

AB22

Not Connected Pins

A2

A6

A12

B11

B16

C2

D1

D4

D18

D19

E17

E19

G2

G22

L2

L19

M2

M21

R3

R20

U3

U18

V6

W4

W19

Y5

Y22

AA1

AA3

AA11

AA16

AB7

AB12

AB21

-

11/02/00

Additional XC2S200 Package Pins (Continued)

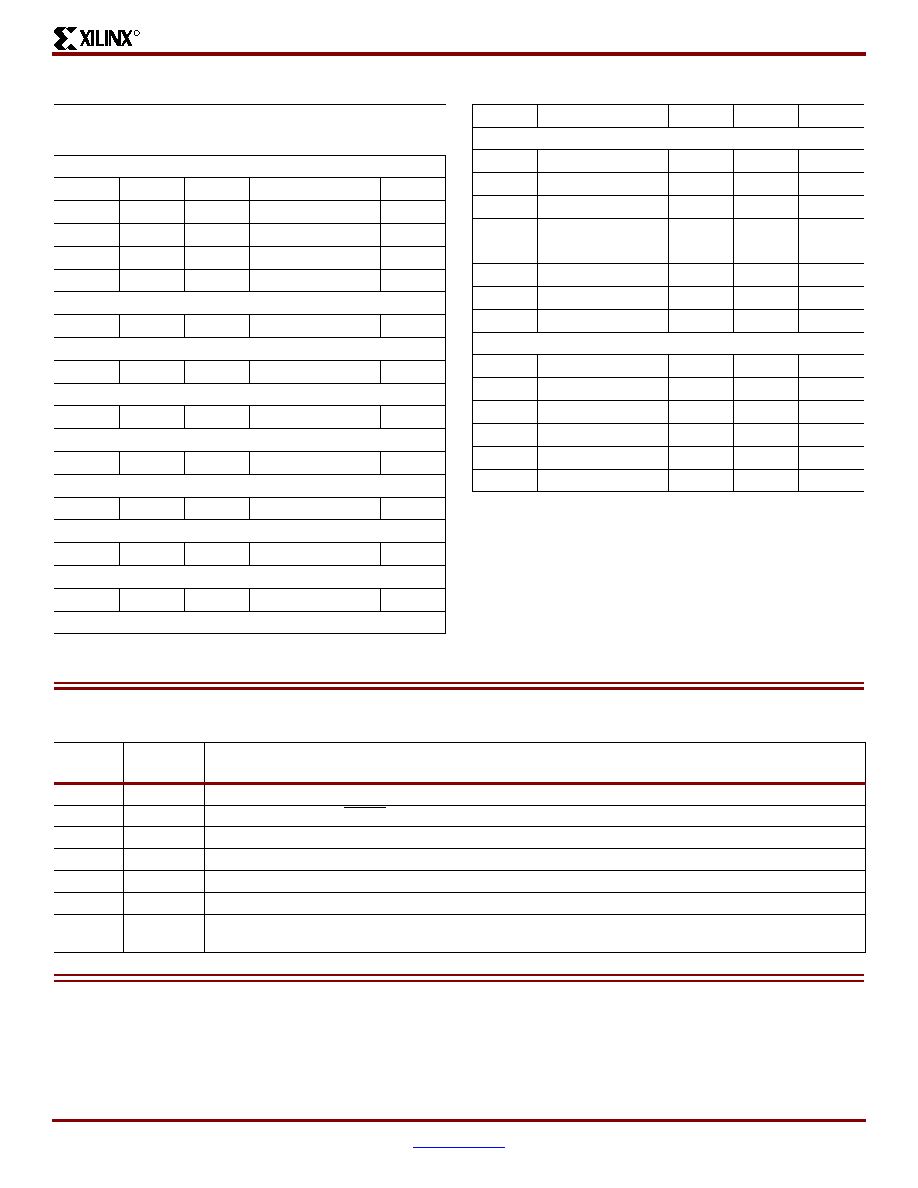

Version

No.

Date

Description

2.0

09/18/00

Sectioned the Spartan-II Family data sheet into four modules. Corrected all known errors in the pinout tables.

2.1

10/04/00

Added notes requiring PWDN to be tied to VCCINT when unused.

2.2

11/02/00

Removed the Power Down feature.

2.3

03/05/01

Added notes on pinout tables for IRDY and TRDY.

2.4

04/30/01

Reinstated XC2S50 VCCO Bank 7, GND, and "not connected" pins missing in version 2.3.

2.5

09/03/03

Added caution about Not Connected Pins to XC2S30 pinout tables on page 76.

2.8

06/13/08

Added "Package Overview" section. Added notes to clarify shared VCCO banks. Updated description and links.

Updated all modules for continuous page, figure, and table numbering. Synchronized all modules to v2.8.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 24LC16B-I/MC | IC EEPROM 16KBIT 400KHZ 8DFN |

| 748610-4 | CONN D-SUB SOCKET 22-28AWG AU |

| XC6SLX4-3CPG196C | IC FPGA SPARTAN 6 3K 196CPGBGA |

| XC6SLX4-L1TQG144C | IC FPAG SPARTAN 6 3K 144TQFP |

| 24LC014H-E/ST | IC EEPROM 1KBIT 400KHZ 8TSSOP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC2S50-5TQ144C-ES | 制造商:Xilinx 功能描述:2S50-5TQ144C-ES |

| XC2S50-5TQ144I | 功能描述:IC FPGA 2.5V I-TEMP 144-TQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:Spartan®-II 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計(jì):2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XC2S50-5TQG144C | 功能描述:IC SPARTAN-II FPGA 50K 144-TQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:Spartan®-II 標(biāo)準(zhǔn)包裝:60 系列:XP LAB/CLB數(shù):- 邏輯元件/單元數(shù):10000 RAM 位總計(jì):221184 輸入/輸出數(shù):244 門數(shù):- 電源電壓:1.71 V ~ 3.465 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:388-BBGA 供應(yīng)商設(shè)備封裝:388-FPBGA(23x23) 其它名稱:220-1241 |

| XC2S50-5TQG144I | 制造商:Xilinx 功能描述:FPGA SPARTAN-II 50K GATES 1728 CELLS 263MHZ 2.5V 144TQFP EP - Trays 制造商:Xilinx 功能描述:IC SYSTEM GATE |

| XC2S50-5VQ100C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-II 2.5V FPGA Family:Introduction and Ordering Information |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。