- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄4159 > XC4013E-1BG225C (Xilinx Inc)IC FPGA C-TEMP 5V 1SPD 225-PBGA PDF資料下載

參數(shù)資料

| 型號(hào): | XC4013E-1BG225C |

| 廠商: | Xilinx Inc |

| 文件頁(yè)數(shù): | 41/68頁(yè) |

| 文件大小: | 0K |

| 描述: | IC FPGA C-TEMP 5V 1SPD 225-PBGA |

| 產(chǎn)品變化通告: | Product Discontinuation 28/Jul/2010 |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | XC4000E/X |

| LAB/CLB數(shù): | 576 |

| 邏輯元件/單元數(shù): | 1368 |

| RAM 位總計(jì): | 18432 |

| 輸入/輸出數(shù): | 192 |

| 門(mén)數(shù): | 13000 |

| 電源電壓: | 4.75 V ~ 5.25 V |

| 安裝類(lèi)型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 225-BBGA |

| 供應(yīng)商設(shè)備封裝: | 225-PBGA |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)當(dāng)前第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)

R

XC4000E and XC4000X Series Field Programmable Gate Arrays

6-50

May 14, 1999 (Version 1.6)

used), and if RAM is present, the RAM content must be

unchanged.

Statistically, one error out of 2048 might go undetected.

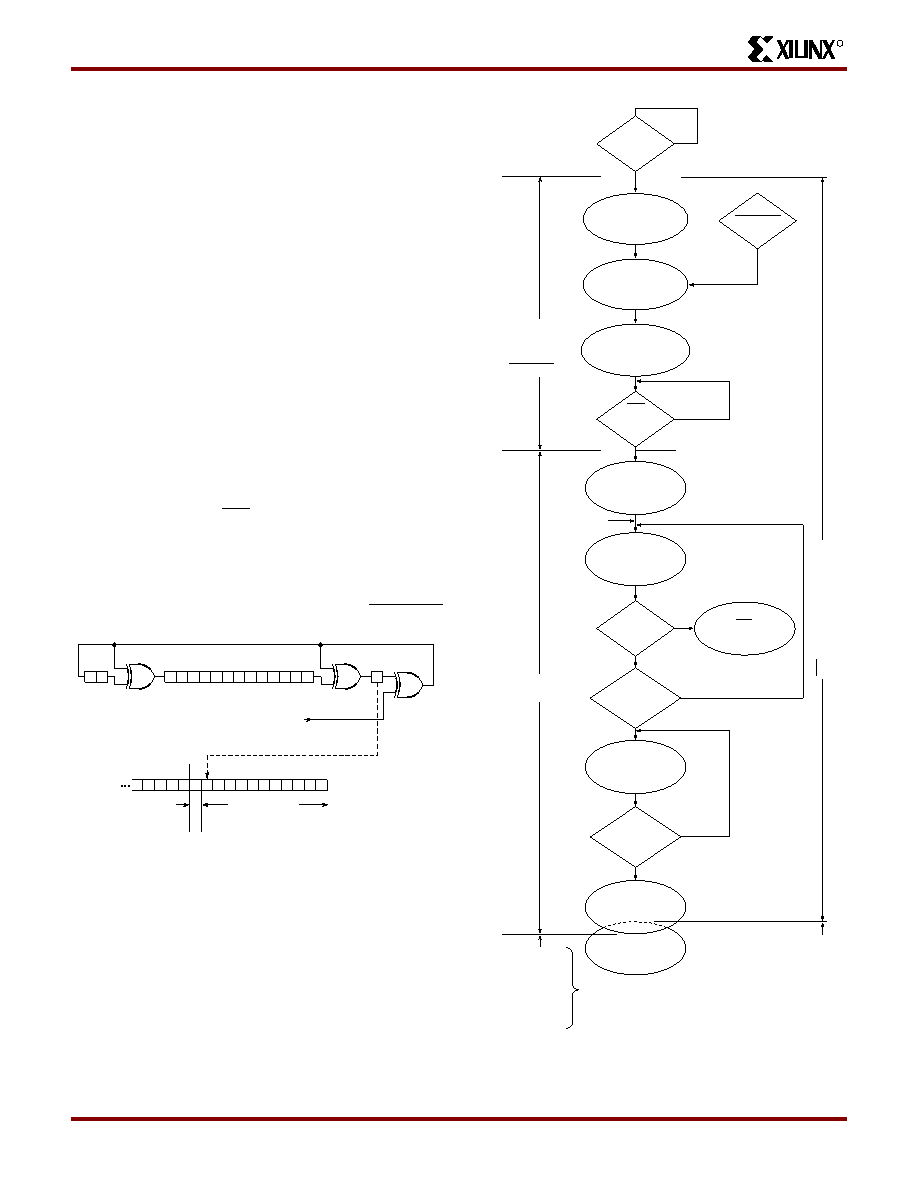

Conguration Sequence

There are four major steps in the XC4000 Series power-up

conguration sequence.

Conguration Memory Clear

Initialization

Conguration

Start-Up

The full process is illustrated in Figure 46.

Conguration Memory Clear

When power is rst applied or is reapplied to an FPGA, an

internal circuit forces initialization of the conguration logic.

When Vcc reaches an operational level, and the circuit

passes the write and read test of a sample pair of congu-

ration bits, a time delay is started. This time delay is nomi-

nally 16 ms, and up to 10% longer in the low-voltage

devices. The delay is four times as long when in Master

Modes (M0 Low), to allow ample time for all slaves to reach

a stable Vcc. When all INIT pins are tied together, as rec-

ommended, the longest delay takes precedence. There-

fore, devices with different time delays can easily be mixed

and matched in a daisy chain.

This delay is applied only on power-up. It is not applied

when re-conguring an FPGA by pulsing the PROGRAM

pin

0

X2

2 3456789 10 11 12 13 14

1

X15

X16

15

SERIAL DATA IN

1 0 1514 13 12 1110 9 8 7 65

1

CRC – CHECKSUM

LAST DATA FRAME

START

BIT

X1789

Polynomial: X16 + X15 + X2 + 1

Readback Data Stream

Figure 45: Circuit for Generating CRC-16

INIT

High? if

Master

Sample

Mode Lines

Load One

Configuration

Data Frame

Frame

Error

Pass

Configuration

Data to DOUT

VCC

>3.5 V

No

Yes

No

Yes

Operational

Start-Up

Sequence

No

Yes

~1.3

s per Frame

Master Waits 50 to 250

s

Before Sampling Mode Lines

Master CCLK

Goes Active

F

Pull INIT Low

and Stop

X6076

EXTEST*

SAMPLE/PRELOAD

BYPASS

CONFIGURE*

(* if PROGRAM = High)

SAMPLE/PRELOAD

BYPASS

EXTEST

SAMPLE PRELOAD

BYPASS

USER 1

USER 2

CONFIGURE

READBACK

If Boundary Scan

is Selected

Config-

uration

memory

Full

CCLK

Count Equals

Length

Count

Completely Clear

Configuration Memory

Once More

LDC

Output

=

L,

HDC

Output

=

H

Boundary Scan

Instructions

Available:

I/O

Active

Keep Clearing

Configuration Memory

Test M0 Generate

One Time-Out Pulse

of 16 or 64 ms

PROGRAM

= Low

No

Yes

Figure 46: Power-up Conguration Sequence

Product Obsolete or Under Obsolescence

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AMC44DRTN-S734 | CONN EDGECARD 88POS DIP .100 SLD |

| 65801-009LF | CONN RCPT 9POS 2.54MM VERT TIN |

| AMC44DRTH-S734 | CONN EDGECARD 88POS DIP .100 SLD |

| AMC44DREN-S734 | CONN EDGECARD 88POS .100 EYELET |

| 65801-006LF | CONN RCPT 6POS 2.54MM VERT TIN |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC4013E-1BG225I | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| XC4013E-1BG240C | 制造商:XILINX 制造商全稱(chēng):XILINX 功能描述:XC4000E and XC4000X Series Field Programmable Gate Arrays |

| XC4013E-1BG240I | 制造商:XILINX 制造商全稱(chēng):XILINX 功能描述:XC4000E and XC4000X Series Field Programmable Gate Arrays |

| XC4013E-1BG240M | 制造商:XILINX 制造商全稱(chēng):XILINX 功能描述:XC4000E and XC4000X Series Field Programmable Gate Arrays |

| XC4013E-1CB240C | 制造商:XILINX 制造商全稱(chēng):XILINX 功能描述:XC4000E and XC4000X Series Field Programmable Gate Arrays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。