- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4175 > XC4028EX-2HQ208C (Xilinx Inc)IC FPGA 1024 CLB'S 208-HQFP PDF資料下載

參數(shù)資料

| 型號(hào): | XC4028EX-2HQ208C |

| 廠商: | Xilinx Inc |

| 文件頁(yè)數(shù): | 38/68頁(yè) |

| 文件大小: | 0K |

| 描述: | IC FPGA 1024 CLB'S 208-HQFP |

| 標(biāo)準(zhǔn)包裝: | 24 |

| 系列: | XC4000E/X |

| LAB/CLB數(shù): | 1024 |

| 邏輯元件/單元數(shù): | 2432 |

| RAM 位總計(jì): | 32768 |

| 輸入/輸出數(shù): | 160 |

| 門數(shù): | 28000 |

| 電源電壓: | 4.75 V ~ 5.25 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 208-BFQFP 裸露焊盤 |

| 供應(yīng)商設(shè)備封裝: | 208-PQFP(28x28) |

| 其它名稱: | 122-1126 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)當(dāng)前第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)

R

May 14, 1999 (Version 1.6)

6-47

XC4000E and XC4000X Series Field Programmable Gate Arrays

6

is passed through and is captured by each FPGA when it

recognizes the 0010 preamble. Following the length-count

data, each FPGA outputs a High on DOUT until it has

received its required number of data frames.

After an FPGA has received its conguration data, it

passes on any additional frame start bits and conguration

data on DOUT. When the total number of conguration

clocks applied after memory initialization equals the value

of the 24-bit length count, the FPGAs begin the start-up

sequence and become operational together. FPGA I/O are

normally released two CCLK cycles after the last congura-

tion bit is received. Figure 47 on page 53 shows the

start-up timing for an XC4000 Series device.

The daisy-chained bitstream is not simply a concatenation

of the individual bitstreams. The PROM le formatter must

be used to combine the bitstreams for a daisy-chained con-

guration.

Multi-Family Daisy Chain

All Xilinx FPGAs of the XC2000, XC3000, and XC4000

Series use a compatible bitstream format and can, there-

fore, be connected in a daisy chain in an arbitrary

sequence. There is, however, one limitation. The lead

device must belong to the highest family in the chain. If the

chain contains XC4000 Series devices, the master nor-

mally cannot be an XC2000 or XC3000 device.

The reason for this rule is shown in Figure 47 on page 53.

Since all devices in the chain store the same length count

value and generate or receive one common sequence of

CCLK pulses, they all recognize length-count match on the

same CCLK edge, as indicated on the left edge of

Figure 47. The master device then generates additional

CCLK pulses until it reaches its nish point F. The different

families generate or require different numbers of additional

CCLK pulses until they reach F. Not reaching F means that

the device does not really nish its conguration, although

DONE may have gone High, the outputs became active,

and the internal reset was released. For the XC4000 Series

device, not reaching F means that readback cannot be ini-

tiated and most boundary scan instructions cannot be

used.

The user has some control over the relative timing of these

events and can, therefore, make sure that they occur at the

proper time and the nish point F is reached. Timing is con-

trolled using options in the bitstream generation software.

XC3000 Master with an XC4000 Series Slave

Some designers want to use an inexpensive lead device in

peripheral mode and have the more precious I/O pins of the

XC4000 Series devices all available for user I/O. Figure 44

provides a solution for that case.

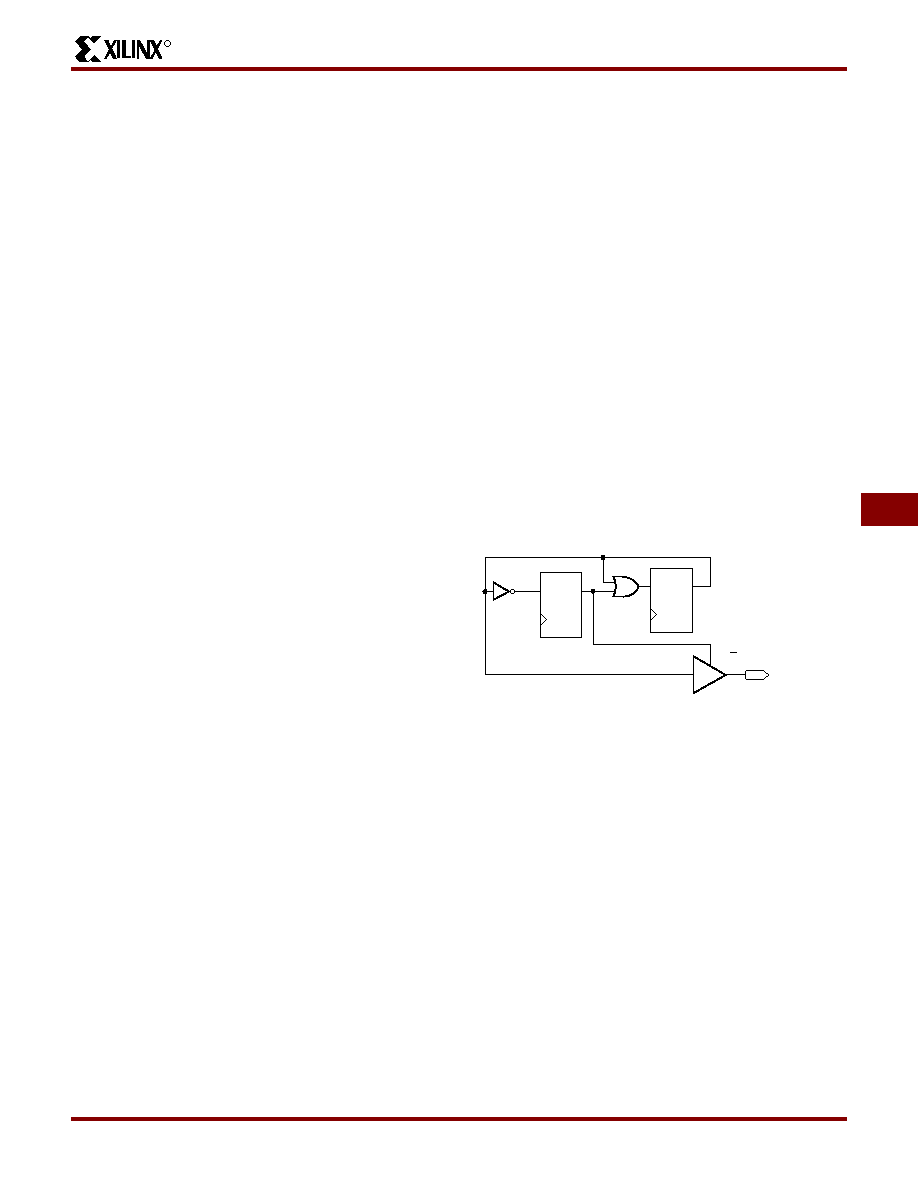

This solution requires one CLB, one IOB and pin, and an

internal oscillator with a frequency of up to 5 MHz as a

clock source. The XC3000 master device must be cong-

ured with late Internal Reset, which is the default option.

One CLB and one IOB in the lead XC3000-family device

are used to generate the additional CCLK pulse required by

the XC4000 Series devices. When the lead device removes

the internal RESET signal, the 2-bit shift register responds

to its clock input and generates an active Low output signal

for the duration of the subsequent clock period. An external

connection between this output and CCLK thus creates the

extra CCLK pulse.

Output

Connected

to CCLK

OE/T

0

1

0

.

0

1

.

Reset

X5223

etc

Active Low Output

Active High Output

Figure 44: CCLK Generation for XC3000 Master

Driving an XC4000 Series Slave

Product Obsolete or Under Obsolescence

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT71V424L15PHGI8 | IC SRAM 4MBIT 15NS 44TSOP |

| IDT7164S25YGI | IC SRAM 64KBIT 25NS 28SOJ |

| XC4025E-3HQ240C | IC FPGA 1024 CLB'S 240-HQFP |

| XC4013E-3PQ160C | IC FPGA 576 CLB'S 160-PQFP |

| XC4010E-4PQ208C | IC FPGA 400 CLB'S 208-PQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC4028EX-2HQ240C | 制造商:Xilinx 功能描述: |

| XC4028EX-3HQ208C | 功能描述:IC FPGA 1024 CLB'S 208-HQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:XC4000E/X 產(chǎn)品變化通告:XC4000(E,L) Discontinuation 01/April/2002 標(biāo)準(zhǔn)包裝:24 系列:XC4000E/X LAB/CLB數(shù):100 邏輯元件/單元數(shù):238 RAM 位總計(jì):3200 輸入/輸出數(shù):80 門數(shù):3000 電源電壓:4.5 V ~ 5.5 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:120-BCBGA 供應(yīng)商設(shè)備封裝:120-CPGA(34.55x34.55) |

| XC4028EX-3HQ208I | 制造商:Xilinx 功能描述: |

| XC4028EX-3HQ240C | 制造商:Xilinx 功能描述: |

| XC4028EX-3HQ240I | 制造商:Xilinx 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。