- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4174 > XC5206-5PQ160C (Xilinx Inc)IC FPGA 196 CLB'S 160-PQFP PDF資料下載

參數(shù)資料

| 型號: | XC5206-5PQ160C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 67/73頁 |

| 文件大小: | 0K |

| 描述: | IC FPGA 196 CLB'S 160-PQFP |

| 產(chǎn)品變化通告: | XC1700 PROMs,XC5200,HQ,SCD Parts Discontinuation 19/Jul/2010 |

| 標準包裝: | 24 |

| 系列: | XC5200 |

| LAB/CLB數(shù): | 196 |

| 邏輯元件/單元數(shù): | 784 |

| 輸入/輸出數(shù): | 133 |

| 門數(shù): | 10000 |

| 電源電壓: | 4.75 V ~ 5.25 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 160-BQFP |

| 供應(yīng)商設(shè)備封裝: | 160-PQFP(28x28) |

| 其它名稱: | 122-1140 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁當前第67頁第68頁第69頁第70頁第71頁第72頁第73頁

R

November 5, 1998 (Version 5.2)

7-89

XC5200 Series Field Programmable Gate Arrays

7

tomized RPMs, freeing the designer from the need to

become an expert on architectures.

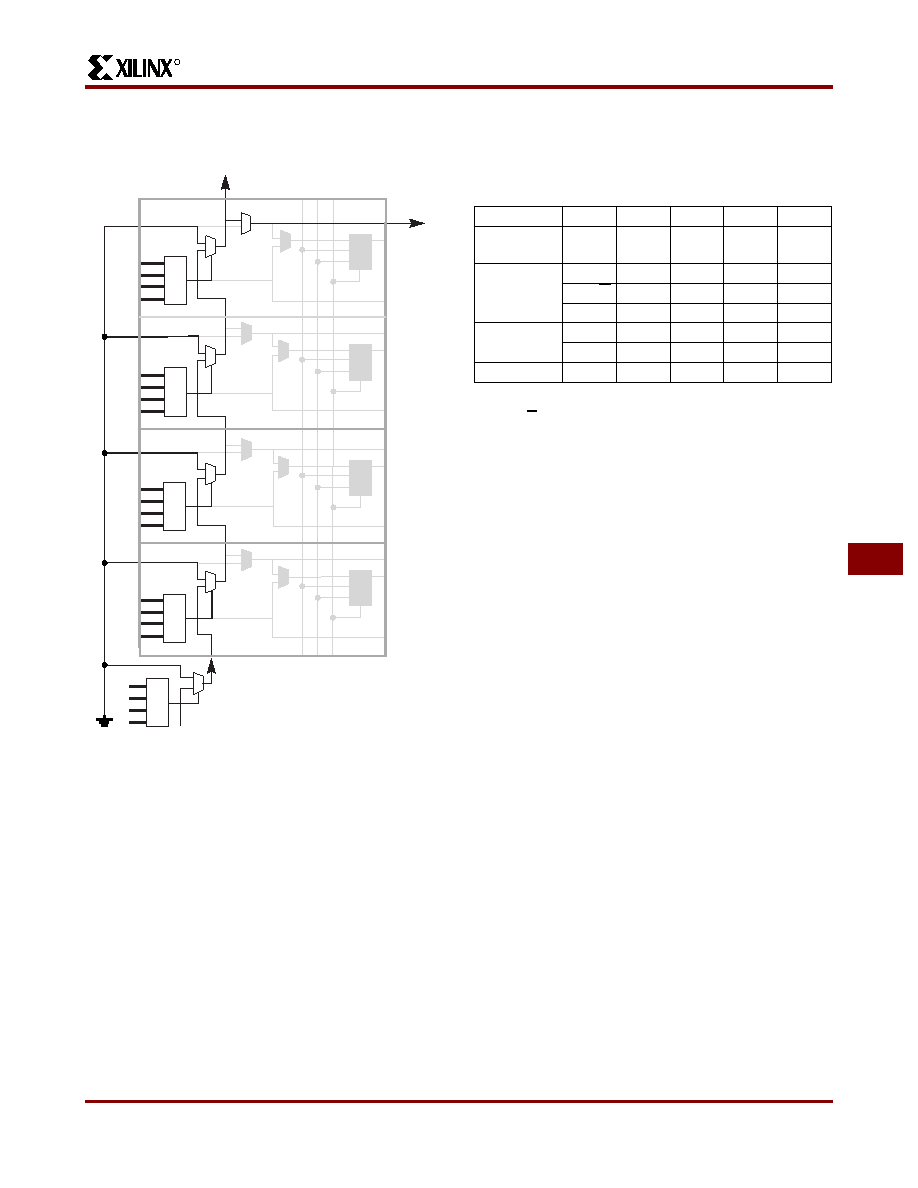

Cascade Function

Each CY_MUX can be connected to the CY_MUX in the

adjacent LC to provide cascadable decode logic. Figure 7

illustrates how the 4-input function generators can be con-

figured to take advantage of these four cascaded

CY_MUXes. Note that AND and OR cascading are specific

cases of a general decode. In AND cascading all bits are

decoded equal to logic one, while in OR cascading all bits

are decoded equal to logic zero. The flexibility of the LUT

achieves this result. The XC5200 library contains gate

macros designed to take advantage of this function.

CLB Flip-Flops and Latches

The CLB can pass the combinatorial output(s) to the inter-

connect network, but can also store the combinatorial

results or other incoming data in flip-flops, and connect

their outputs to the interconnect network as well. The CLB

storage elements can also be configured as latches.

Data Inputs and Outputs

The source of a storage element data input is programma-

ble. It is driven by the function F, or by the Direct In (DI)

block input. The flip-flops or latches drive the Q CLB out-

puts.

Four fast feed-through paths from DI to DO are available,

as shown in Figure 4. This bypass is sometimes used by

the automated router to repower internal signals. In addi-

tion to the storage element (Q) and direct (DO) outputs,

there is a combinatorial output (X) that is always sourced

by the Lookup Table.

The four edge-triggered D-type flip-flops or level-sensitive

latches have common clock (CK) and clock enable (CE)

inputs. Any of the clock inputs can also be permanently

enabled. Storage element functionality is described in

Clock Input

The flip-flops can be triggered on either the rising or falling

clock edge. The clock pin is shared by all four storage ele-

ments with individual polarity control. Any inverter placed

on the clock input is automatically absorbed into the CLB.

Clock Enable

The clock enable signal (CE) is active High. The CE pin is

shared by the four storage elements. If left unconnected

for any, the clock enable for that storage element defaults

to the active state. CE is not invertible within the CLB.

Clear

An asynchronous storage element input (CLR) can be used

to reset all four flip-flops or latches in the CLB. This input

Figure 7: XC5200 CY_MUX Used for Decoder Cascade

Logic

F4

F3

F2

F1

F4

F3

F2

F1

F4

F3

F2

F1

F4

F3

F2

F1

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

AND

F=0

DI

FD

cascade out

out

DO

D

X

LC3

DO

DQ

LC2

X

CI

cascade in

CY_MUX

FD

X

LC1

Initialization of

carry chain (One Logic Cell)

LC0

CK

CE

CLR

D

Q

X

Q

CO

AND

X5708

Table 3: CLB Storage Element Functionality

(active rising edge is shown)

Mode

CK

CE

CLR

D

Q

Power-Up or

GR

XXXX

0

Flip-Flop

XX

1

X

0

__/

1*

0*

D

0X

0*

X

Q

Latch

11*

0*

X

Q

01*

0*

D

Both

X

0

0*

X

Q

Legend:

X

__/

0*

1*

Don’t care

Rising edge

Input is Low or unconnected (default value)

Input is High or unconnected (default value)

Product Obsolete or Under Obsolescence

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ACB65DHAS | CONN EDGECARD 130PS R/A .050 DIP |

| XC5206-6PQ100C | IC FPGA 196 CLB'S 100-PQFP |

| AMM28DTMT-S189 | CONN EDGECARD 56POS R/A .156 SLD |

| XC5206-5PC84C | IC FPGA 196 CLB'S 84-PLCC |

| XC5204-6VQ100C | IC FPGA 120 CLB'S 100-VQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC5206-5PQ160I | 制造商:Xilinx 功能描述: |

| XC5206-5PQ208C | 功能描述:IC FPGA 196 CLB'S 208-PQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:XC5200 產(chǎn)品變化通告:XC4000(E,L) Discontinuation 01/April/2002 標準包裝:24 系列:XC4000E/X LAB/CLB數(shù):100 邏輯元件/單元數(shù):238 RAM 位總計:3200 輸入/輸出數(shù):80 門數(shù):3000 電源電壓:4.5 V ~ 5.5 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:120-BCBGA 供應(yīng)商設(shè)備封裝:120-CPGA(34.55x34.55) |

| XC5206-5PQ208C0262 | 制造商:Xilinx 功能描述: |

| XC5206-5PQ208I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| XC5206-5PQ240C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

發(fā)布緊急采購,3分鐘左右您將得到回復。