- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371341 > XC5210-3TQ144I Field Programmable Gate Array (FPGA) PDF資料下載

參數(shù)資料

| 型號(hào): | XC5210-3TQ144I |

| 英文描述: | Field Programmable Gate Array (FPGA) |

| 中文描述: | 現(xiàn)場可編程門陣列(FPGA) |

| 文件頁數(shù): | 6/73頁 |

| 文件大?。?/td> | 598K |

| 代理商: | XC5210-3TQ144I |

第1頁第2頁第3頁第4頁第5頁當(dāng)前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁

R

XC5200 Series Field Programmable Gate Arrays

7-88

November 5, 1998 (Version 5.2)

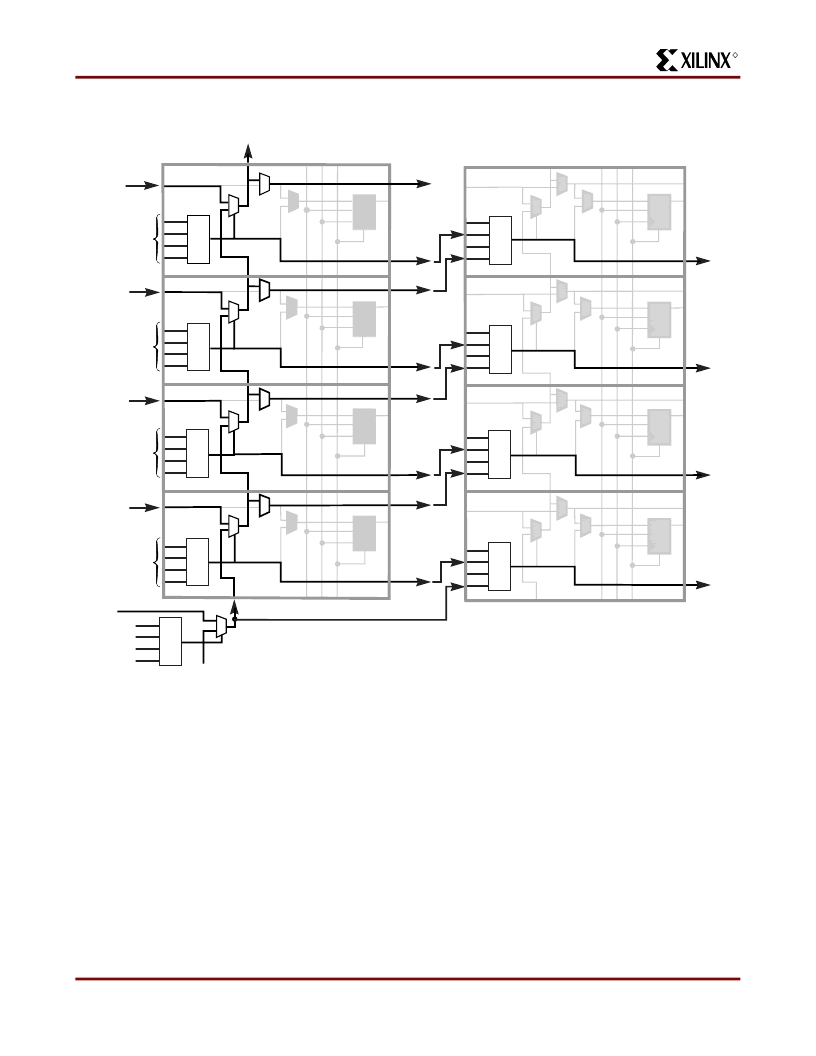

Carry Function

The XC5200 family supports a carry-logic feature that

enhances the performance of arithmetic functions such as

counters, adders, etc. A carry multiplexer (CY_MUX) sym-

bol is used to indicate the XC5200 carry logic. This symbol

represents the dedicated 2:1 multiplexer in each LC that

performs the one-bit high-speed carry propagate per logic

cell (four bits per CLB).

While the carry propagate is performed inside the LC, an

adjacent LC must be used to complete the arithmetic func-

tion.

Figure 6

represents an example of an adder function.

The carry propagate is performed on the CLB shown,

which also generates the half-sum for the four-bit adder. An

adjacent CLB is responsible for XORing the half-sum with

the corresponding carry-out. Thus an adder or counter

requires two LCs per bit. Notice that the carry chain

requires an initialization stage, which the XC5200 family

accomplishes using the carry initialize (CY_INIT) macro

and one additional LC. The carry chain can propagate ver-

tically up a column of CLBs.

The XC5200 library contains a set of Relationally-Placed

Macros (RPMs) and arithmetic functions designed to take

advantage of the dedicated carry logic. Using and modify-

ing these macros makes it much easier to implement cus-

Figure 6: XC5200 CY_MUX Used for Adder Carry Propagate

F4

F3

F2

F1

F4

F3

F2

F1

F4

F3

F2

F1

F4

F3

F2

F1

XOR

XOR

XOR

XOR

F=0

DI

DI

DI

DI

FD

FD

FD

FD

carry out

carry3

DO

D

X

LC3

DO

D

Q

LC2

DO

X

CI

carry in

CY_MUX

CY_MUX

CY_MUX

CY_MUX

CY_MUX

X

DO

DO

Q

DO

LC1

LC0

CK

CE

CLR

D

D

Q

Q

X

Q

half sum0

carry0

half sum2

half sum1

carry1

carry2

half sum3

CO

A3

or

B3

A3 and B3

to any two

A2 and B2

to any two

A2

or

B2

A1

or

B1

A1 and B1

to any two

A0

or

B0

A0 and B0

to any two

0

F4

F3

F2

F1

F4

F3

F2

F1

F4

F3

F2

F1

F4

F3

F2

F1

XOR

XOR

XOR

XOR

DI

DI

DI

DI

FD

FD

DO

FD

FD

D

X

LC3

DO

D

Q

LC2

X

CI

X

LC1

LC0

CK

CE

CLR

D

D

Q

X

Q

sum0

sum2

sum1

sum3

CO

Initialization of

carry chain (One Logic Cell)

X5709

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC5210-3TQ176I | Field Programmable Gate Array (FPGA) |

| XC5210-4BG225I | Field Programmable Gate Array (FPGA) |

| XC5210-4PC84I | Field Programmable Gate Array (FPGA) |

| XC5210-4TQ176I | Field Programmable Gate Array (FPGA) |

| XC5210-5PC84I | Field Programmable Gate Array (FPGA) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC5210-3TQ176C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5210-3TQ176I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| XC5210-3VQ100C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5210-3VQ64C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5210-4BG225C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。