- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371341 > XC5210-5PQ240I Field Programmable Gate Array (FPGA) PDF資料下載

參數(shù)資料

| 型號: | XC5210-5PQ240I |

| 英文描述: | Field Programmable Gate Array (FPGA) |

| 中文描述: | 現(xiàn)場可編程門陣列(FPGA) |

| 文件頁數(shù): | 18/73頁 |

| 文件大小: | 598K |

| 代理商: | XC5210-5PQ240I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當(dāng)前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁

R

XC5200 Series Field Programmable Gate Arrays

7-100

November 5, 1998 (Version 5.2)

XC5200-Series devices can also be configured through the

boundary scan logic. See XAPP 017 for more information.

Data Registers

The primary data register is the boundary scan register.

For each IOB pin in the FPGA, bonded or not, it includes

three bits for In, Out and 3-State Control. Non-IOB pins

have appropriate partial bit population for In or Out only.

PROGRAM, CCLK and DONE are not included in the

boundary scan register. Each EXTEST CAPTURE-DR

state captures all In, Out, and 3-State pins.

The data register also includes the following non-pin bits:

TDO.T, and TDO.O, which are always bits 0 and 1 of the

data register, respectively, and BSCANT.UPD, which is

always the last bit of the data register. These three bound-

ary scan bits are special-purpose Xilinx test signals.

The other standard data register is the single flip-flop

BYPASS register. It synchronizes data being passed

through the FPGA to the next downstream boundary scan

device.

The FPGA provides two additional data registers that can

be specified using the BSCAN macro. The FPGA provides

two user pins (BSCAN.SEL1 and BSCAN.SEL2) which are

the decodes of two user instructions, USER1 and USER2.

For

these

instructions,

(BSCAN.TDO1 and BSCAN.TDO2) allow user scan data to

be shifted out on TDO. The data register clock

(BSCAN.DRCK) is available for control of test logic which

the user may wish to implement with CLBs. The NAND of

TCK and RUN-TEST-IDLE is also provided (BSCAN.IDLE).

two

corresponding

pins

Instruction Set

The XC5200-Series boundary scan instruction set also

includes instructions to configure the device and read back

the configuration data. The instruction set is coded as

shown in

Table 7

.

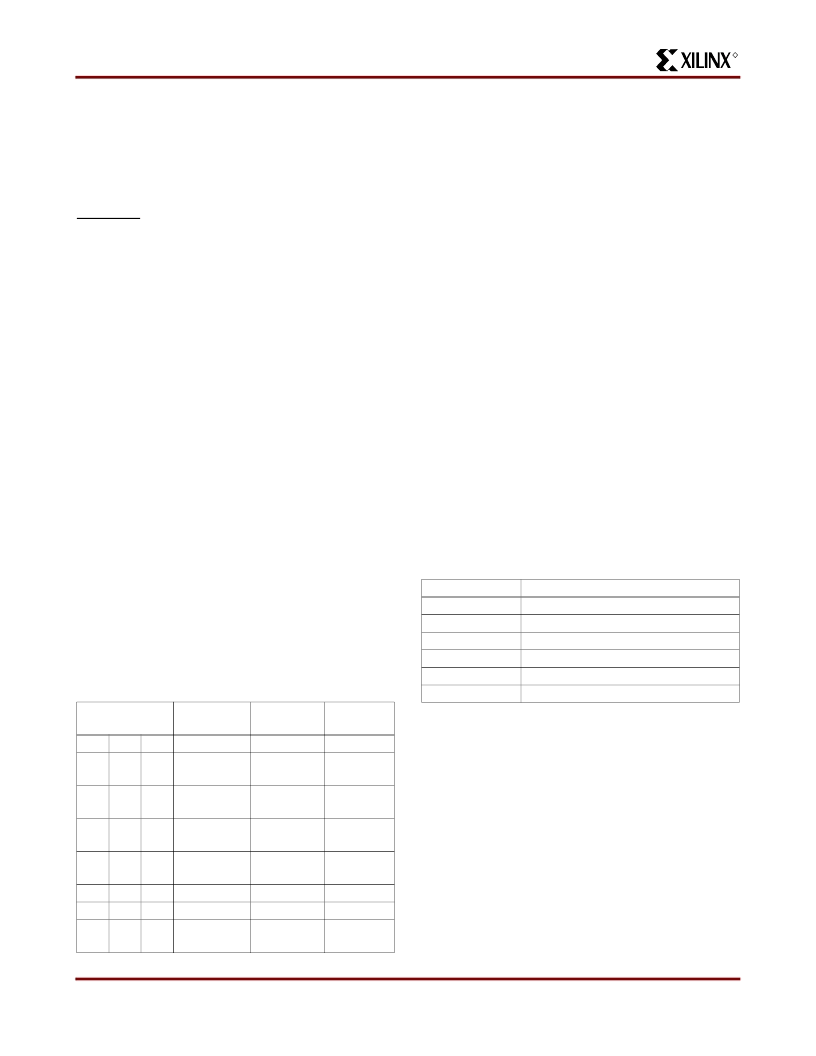

Table 7: Boundary Scan Instructions

Bit Sequence

The bit sequence within each IOB is: 3-State, Out, In. The

data-register cells for the TAP pins TMS, TCK, and TDI

have an OR-gate that permanently disables the output

buffer if boundary-scan operation is selected. Conse-

quently, it is impossible for the outputs in IOBs used by TAP

inputs to conflict with TAP operation. TAP data is taken

directly from the pin, and cannot be overwritten by injected

boundary-scan data.

The primary global clock inputs (PGCK1-PGCK4) are

taken directly from the pins, and cannot be overwritten with

boundary-scan data. However, if necessary, it is possible to

drive the clock input from boundary scan. The external

clock source is 3-stated, and the clock net is driven with

boundary scan data through the output driver in the

clock-pad IOB. If the clock-pad IOBs are used for non-clock

signals, the data may be overwritten normally.

Pull-up and pull-down resistors remain active during

boundary scan. Before and during configuration, all pins

are pulled up. After configuration, the choice of internal

pull-up or pull-down resistor must be taken into account

when designing test vectors to detect open-circuit PC

traces.

From a cavity-up view of the chip (as shown in XDE or

Epic), starting in the upper right chip corner, the boundary

scan data-register bits are ordered as shown in

Table 8

.

The device-specific pinout tables for the XC5200 Series

include the boundary scan locations for each IOB pin.

Table 8: Boundary Scan Bit Sequence

BSDL (Boundary Scan Description Language) files for

XC5200-Series devices are available on the Xilinx web site

in the File Download area.

Including Boundary Scan

If boundary scan is only to be used during configuration, no

special elements need be included in the schematic or HDL

code. In this case, the special boundary scan pins TDI,

TMS, TCK and TDO can be used for user functions after

configuration.

To indicate that boundary scan remain enabled after config-

uration, include the BSCAN library symbol and connect pad

symbols to the TDI, TMS, TCK and TDO pins, as shown in

Figure 20

.

Instruction I2

I1 I0

0

0

0

0

Test

Selected

EXTEST

SAMPLE/PR

ELOAD

USER 1

TDO Source

I/O Data

Source

DR

Pin/Logic

0

1

DR

DR

0

1

0

BSCAN.

TDO1

BSCAN.

TDO2

User Logic

0

1

1

USER 2

User Logic

1

0

0

READBACK Readback

Data

DOUT

—

Bypass

Register

Pin/Logic

1

1

1

0

1

1

1

0

1

CONFIGURE

Reserved

BYPASS

Disabled

—

—

Bit Position

Bit 0 (TDO)

Bit 1

...

...

...

Bit N (TDI)

I/O Pad Location

Top-edge I/O pads (right to left)

...

Left-edge I/O pads (top to bottom)

Bottom-edge I/O pads (left to right)

Right-edge I/O pads (bottom to top)

BSCANT.UPD

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC5210-6PQ160I | Field Programmable Gate Array (FPGA) |

| XC5210-6PQ208I | Field Programmable Gate Array (FPGA) |

| XC5210-6PQ240I | Field Programmable Gate Array (FPGA) |

| XC5215-3BG352I | Field Programmable Gate Array (FPGA) |

| XC5215-3HQ208I | Field Programmable Gate Array (FPGA) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC5210-5PQG208C | 制造商:Rochester Electronics LLC 功能描述: 制造商:Xilinx 功能描述: |

| XC5210-5TQ144C | 制造商:Xilinx 功能描述: |

| XC5210-5TQ144I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| XC5210-5TQ176C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5210-5VQ100C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。