- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371341 > XC5210-6PQ208I Field Programmable Gate Array (FPGA) PDF資料下載

參數(shù)資料

| 型號(hào): | XC5210-6PQ208I |

| 英文描述: | Field Programmable Gate Array (FPGA) |

| 中文描述: | 現(xiàn)場(chǎng)可編程門陣列(FPGA) |

| 文件頁數(shù): | 5/73頁 |

| 文件大小: | 598K |

| 代理商: | XC5210-6PQ208I |

第1頁第2頁第3頁第4頁當(dāng)前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁

R

November 5, 1998 (Version 5.2)

7-87

XC5200 Series Field Programmable Gate Arrays

7

single-length lines, double-length lines, and Longlines all

routed through the GRM. The direct connects, LIM, and

logic-cell

feedthrough

are

Versa-Block. Throughout the XC5200 interconnect, an effi-

cient multiplexing scheme, in combination with three layer

metal (TLM), was used to improve the overall efficiency of

silicon usage.

contained

within

each

Performance Overview

The XC5200 family has been benchmarked with many

designs running synchronous clock rates beyond 66 MHz.

The performance of any design depends on the circuit to be

implemented, and the delay through the combinatorial and

sequential logic elements, plus the delay in the intercon-

nect routing. A rough estimate of timing can be made by

assuming 3-6 ns per logic level, which includes direct-con-

nect routing delays, depending on speed grade. More

accurate estimations can be made using the information in

the Switching Characteristic Guideline section.

Taking Advantage of Reconfiguration

FPGA devices can be reconfigured to change logic function

while resident in the system. This capability gives the sys-

tem designer a new degree of freedom not available with

any other type of logic.

Hardware can be changed as easily as software. Design

updates or modifications are easy, and can be made to

products already in the field. An FPGA can even be recon-

figured dynamically to perform different functions at differ-

ent times.

Reconfigurable logic can be used to implement system

self-diagnostics, create systems capable of being reconfig-

ured for different environments or operations, or implement

multi-purpose hardware for a given application. As an

added benefit, using reconfigurable FPGA devices simpli-

fies hardware design and debugging and shortens product

time-to-market.

Detailed Functional Description

Configurable Logic Blocks (CLBs)

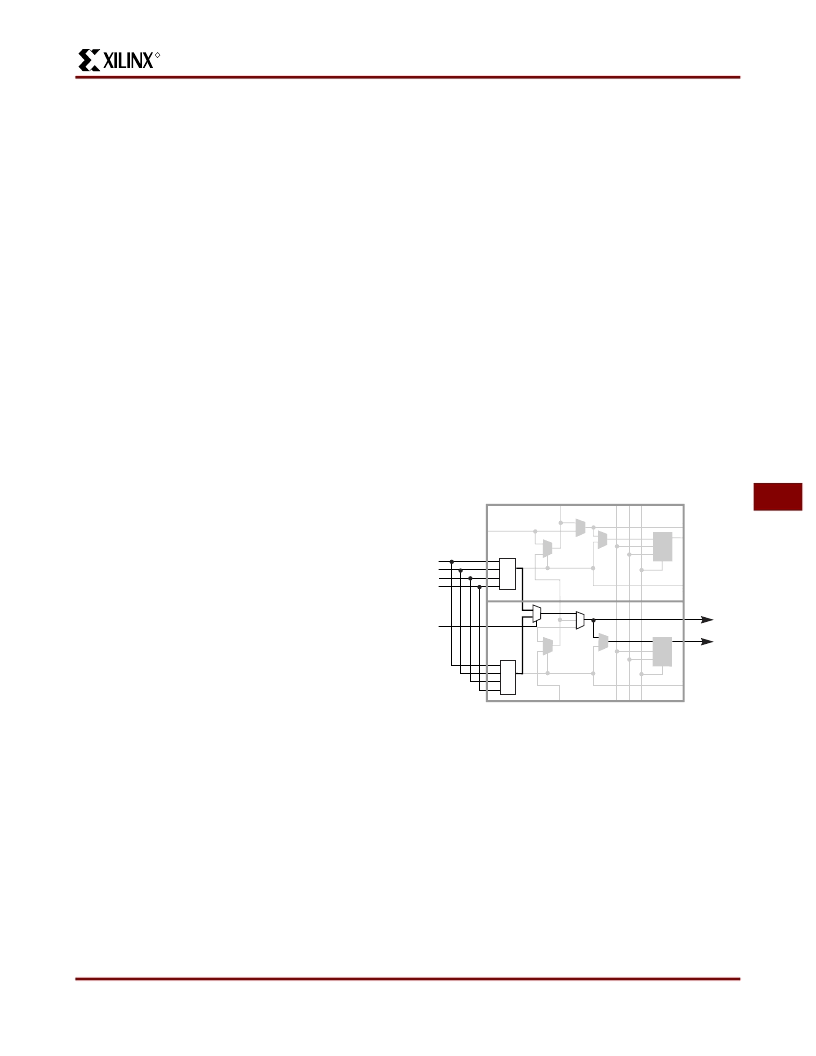

Figure 4

shows the logic in the XC5200 CLB, which con-

sists of four Logic Cells (LC[3:0]). Each Logic Cell consists

of an independent 4-input Lookup Table (LUT), and a

D-Type flip-flop or latch with common clock, clock enable,

and clear, but individually selectable clock polarity. Addi-

tional logic features provided in the CLB are:

An independent 5-input LUT by combining two 4-input

LUTs.

High-speed carry propagate logic.

High-speed pattern decoding.

High-speed direct connection to flip-flop D-inputs.

Individual selection of either a transparent,

level-sensitive latch or a D flip-flop.

Four 3-state buffers with a shared Output Enable.

5-Input Functions

Figure 5

illustrates how the outputs from the LUTs from

LC0 and LC1 can be combined with a 2:1 multiplexer

(F5_MUX) to provide a 5-input function. The outputs from

the LUTs of LC2 and LC3 can be similarly combined.

Figure 5: Two LUTs in Parallel Combined to Create a

5-input Function

out

Q

Qout

DO

Q

D

FD

X

FD

CO

DI

X

CLR

LC0

CK

CE

5-Input Function

D

DO

F5_MUX

DI

F

F4

F3

F2

F1

F4

F3

F2

F1

I1

I2

I3

I4

I5

CI

F

LC1

X5710

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC5210-6PQ240I | Field Programmable Gate Array (FPGA) |

| XC5215-3BG352I | Field Programmable Gate Array (FPGA) |

| XC5215-3HQ208I | Field Programmable Gate Array (FPGA) |

| XC5215-4HQ208I | Field Programmable Gate Array (FPGA) |

| XC5215-4HQ240I | Field Programmable Gate Array (FPGA) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC5210-6PQ240C | 功能描述:IC FPGA 324 CLB'S 240-PQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:XC5200 產(chǎn)品變化通告:XC4000(E,L) Discontinuation 01/April/2002 標(biāo)準(zhǔn)包裝:24 系列:XC4000E/X LAB/CLB數(shù):100 邏輯元件/單元數(shù):238 RAM 位總計(jì):3200 輸入/輸出數(shù):80 門數(shù):3000 電源電壓:4.5 V ~ 5.5 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:120-BCBGA 供應(yīng)商設(shè)備封裝:120-CPGA(34.55x34.55) |

| XC5210-6PQ240I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| XC5210-6PQG208C | 制造商:Xilinx 功能描述: |

| XC52106T144C | 制造商:Xilinx 功能描述: |

| XC5210-6TQ144C | 功能描述:IC FPGA 324 CLB'S 144-TQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:XC5200 產(chǎn)品變化通告:XC4000(E,L) Discontinuation 01/April/2002 標(biāo)準(zhǔn)包裝:24 系列:XC4000E/X LAB/CLB數(shù):100 邏輯元件/單元數(shù):238 RAM 位總計(jì):3200 輸入/輸出數(shù):80 門數(shù):3000 電源電壓:4.5 V ~ 5.5 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:120-BCBGA 供應(yīng)商設(shè)備封裝:120-CPGA(34.55x34.55) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。