- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371341 > XC5215-4HQ240I Field Programmable Gate Array (FPGA) PDF資料下載

參數(shù)資料

| 型號(hào): | XC5215-4HQ240I |

| 英文描述: | Field Programmable Gate Array (FPGA) |

| 中文描述: | 現(xiàn)場(chǎng)可編程門陣列(FPGA) |

| 文件頁(yè)數(shù): | 48/73頁(yè) |

| 文件大小: | 598K |

| 代理商: | XC5215-4HQ240I |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)當(dāng)前第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)

R

XC5200 Series Field Programmable Gate Arrays

7-130

November 5, 1998 (Version 5.2)

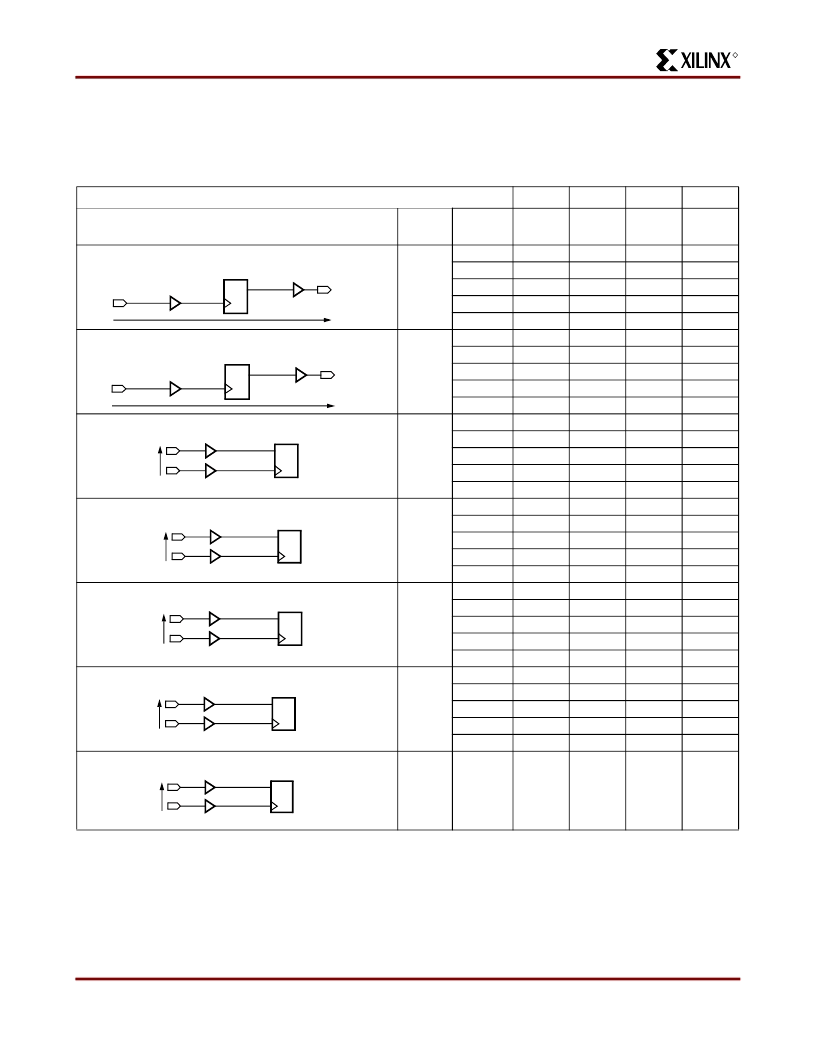

XC5200 Guaranteed Input and Output Parameters (Pin-to-Pin)

All values listed below are tested directly, and guaranteed over the operating conditions. The same parameters can also be

derived indirectly from the Global Buffer specifications. The delay calculator uses this indirect method, and may

overestimate because of worst-case assumptions. When there is a discrepancy between these two methods, the values

listed below should be used, and the derived values should be considered conservative overestimates.

Speed Grade

-6

-5

-4

-3

Description

Symbol

Device

Max

(ns)

16.9

17.1

17.2

17.2

19.0

21.4

21.6

21.7

21.7

24.3

2.5

2.3

2.2

2.2

2.0

3.8

3.9

4.4

5.1

5.8

7.3

7.3

7.2

7.2

6.8

8.8

8.6

8.5

8.5

8.5

0

Max

(ns)

15.1

15.3

15.4

15.4

17.0

18.7

18.9

19.0

19.0

21.2

2.0

1.9

1.9

1.9

1.8

3.8

3.9

4.4

5.1

5.8

6.6

6.6

6.5

6.5

5.7

7.7

7.5

7.4

7.4

7.4

0

Max

(ns)

10.9

11.3

11.9

12.8

12.8

12.6

13.3

13.6

15.0

15.0

1.9

1.9

1.9

1.9

1.7

3.5

3.8

4.4

4.9

5.7

6.6

6.6

6.4

6.0

5.7

7.5

7.5

7.4

7.4

7.4

0

Max

(ns)

9.8

9.9

10.8

11.2

11.7

11.5

11.9

12.5

12.9

13.1

1.9

1.9

1.9

1.8

1.7

3.5

3.6

4.3

4.8

5.6

6.6

6.6

6.3

6.0

5.7

7.5

7.5

7.4

7.3

7.2

0

Global Clock to Output Pad (fast)

T

ICKOF

(Max)

XC5202

XC5204

XC5206

XC5210

XC5215

XC5202

XC5204

XC5206

XC5210

XC5215

XC5202

XC5204

XC5206

XC5210

XC5215

XC5202

XC5204

XC5206

XC5210

XC5215

XC5202

XC5204

XC5206

XC5210

XC5215

XC5202

XC5204

XC5206

XC5210

XC5215

XC52xx

Global Clock to Output Pad (slew-limited)

T

ICKO

(Max)

Input Set-up Time (no delay) to CLB Flip-Flop

IOB

(NODELAY)Connect

T

PSUF

(Min)

Input Hold Time (no delay) to CLB Flip-Flop

IOB

(NODELAY)

T

PHF

(Min)

Input Set-up Time (with delay) to CLB Flip-Flop DI Input

IOB

T

PSU

Input Set-up Time (with delay) to CLB Flip-Flop F Input

IOB

Direct

T

PSU

L

(Min)

Input Hold Time (with delay) to CLB Flip-Flop

IOB

T

PH

(Min)

Note:

1. These measurements assume that the CLB flip-flop uses a direct interconnect to or from the IOB. The INREG/ OUTREG

properties, or XACT-Performance, can be used to assure that direct connects are used. t

applies only to the CLB input

DI that bypasses the look-up table, which only offers direct connects to IOBs on the left and right edges of the die. t

applies to the CLB inputs F that feed the look-up table, which offers direct connect to IOBs on all four edges, as do the CLB

Q outputs.

2. When testing outputs (fast or slew-limited), half of the outputs on one side of the device are switching.

Global Clock-to-Output Delay

Q

.

Direct

IOB

CLB

FAST

BUFG

Global Clock-to-Output Delay

Q

.

Direct

IOB

CLB

BUFG

Time

F,DI

CLB

BUFG

Time

Direct

CLB

F,DI

BUFG

Time

Direct

Connect

CLB

DI

BUFG

Time

CLB

F

BUFG

Time

Direct

CLB

BUFG

F,DI

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC5215-4PG299I | Field Programmable Gate Array (FPGA) |

| XC5215-4PQ160I | Field Programmable Gate Array (FPGA) |

| XC5215-5PG299I | Field Programmable Gate Array (FPGA) |

| XC5215-5PQ160I | Field Programmable Gate Array (FPGA) |

| XC5204 | Field Programmable Gate Arrays(現(xiàn)場(chǎng)可編程門陣列) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC5215-4HQ304I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| XC5215-4PC84C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5215-4PG156C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5215-4PG191C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5215-4PG223C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。