- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1974 > XC95288XV-7TQ144C (Xilinx Inc)IC CPLD 2.5V ISP 144-TQFP PDF資料下載

參數(shù)資料

| 型號: | XC95288XV-7TQ144C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 9/14頁 |

| 文件大小: | 0K |

| 描述: | IC CPLD 2.5V ISP 144-TQFP |

| 產(chǎn)品變化通告: | Product Discontinuation Notice 14/May/2007 |

| 標準包裝: | 60 |

| 系列: | XC9500XV |

| 可編程類型: | 系統(tǒng)內(nèi)可編程 |

| 最大延遲時間 tpd(1): | 7.5ns |

| 電壓電源 - 內(nèi)部: | 2.37 V ~ 2.62 V |

| 邏輯元件/邏輯塊數(shù)目: | 16 |

| 宏單元數(shù): | 288 |

| 門數(shù): | 6400 |

| 輸入/輸出數(shù): | 117 |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 144-LQFP |

| 供應商設備封裝: | 144-TQFP(20x20) |

| 包裝: | 托盤 |

XC95288XV High-Performance CPLD

4

DS050 (v3.0) June 25, 2007

Product Specification

R

Supported I/O Standards

The XC95288XV CPLD features both LVCMOS and LVTTL

I/O implementations. See Table 1 for I/O standard voltages.

The LVTTL I/O standard is a general purpose EIA/JEDEC

standard for 3.3V applications that use an LVTTL input

buffer and Push-Pull output buffer. The LVCMOS2 standard

is used in 2.5V applications.

XC9500XV CPLDs are also 1.8V I/O compatible. The

X25TO18 setting is provided for generating 1.8V compatible

outputs from a CPLD normally operating in a 2.5V environ-

ment. The ISE software automatically groups outputs with

matching IOSTANDARD settings into the same VCCIO bank

when no location constraints are specified. The default I/O

Standard for pads without IOSTANDARD attributes is

LVTTL for XC9500XV devices.

Absolute Maximum Ratings

Recommended Operation Conditions

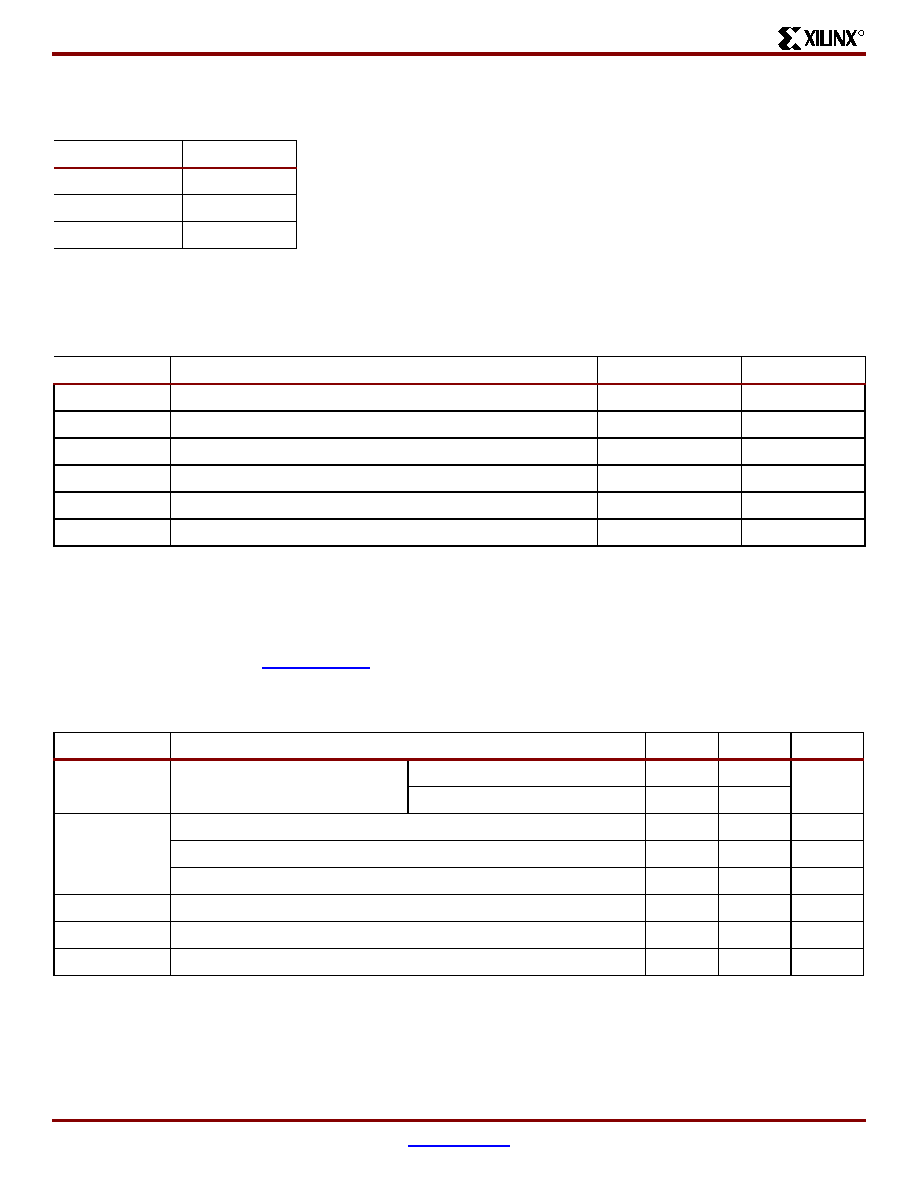

Table 1: IOSTANDARD Options

IOSTANDARD

VCCIO

LVTTL

3.3V

LVCMOS2

2.5V

X25TO18

1.8V

Symbol

Description

Value

Units

VCC

Supply voltage relative to GND

–0.5 to 2.7

V

VCCIO

Supply voltage for output drivers

–0.5 to 3.6

V

VIN

Input voltage relative to GND(1)

–0.5 to 3.6

V

VTS

Voltage applied to 3-state output(1)

–0.5 to 3.6

V

TSTG

Storage temperature (ambient)

–65 to +150

oC

TJ

Junction temperature

+150

oC

Notes:

1.

Maximum DC undershoot below GND must be limited to either 0.5V or 10 mA, whichever is easier to achieve. During transitions, the

device pins may undershoot to –2.0V or overshoot to +3.6V, provided this over- or undershoot lasts less than 10 ns and with the

forcing current being limited to 200 mA.

2.

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress

ratings only, and functional operation of the device at these or any other conditions beyond those listed under Operating Conditions

is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time may affect device reliability.

3.

For solder specifications, see Xilinx Packaging.

Symbol

Parameter

Min

Max

Units

VCCINT

Supply voltage for internal logic

and input buffers

Commercial TA = 0oC to +70oC

2.37

2.62

V

Industrial TA = –40oC to +85oC

2.37

2.62

VCCIO

Supply voltage for output drivers for 3.3V operation

3.0

3.6

V

Supply voltage for output drivers for 2.5V operation

2.37

2.62

V

Supply voltage for output drivers for 1.8V operation

1.71

1.89

V

VIL

Low-level input voltage

0

0.8

V

VIH

High-level input voltage

1.7

3.6

V

VO

Output voltage

0

VCCIO

V

Product Obsolete/Under Obsolescence

相關PDF資料 |

PDF描述 |

|---|---|

| XC9536-5VQG44C | IC CPLD 36MCELL 5NS 44-VQFP |

| XC9536XL-10CSG48I | IC CPLD 36MCELL 10NS 48-CSBGA |

| XC9536XV-7VQ44C | IC CPLD 2.5V ISP 44-VQFP |

| XC9572XL-5TQG100C | IC CPLD 72MCELL 5NS 100-TQFP |

| XC9572XV-7VQ44C | IC CPLD 2.5V ISP 44-VQFP |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| XC95288XV-7TQ144I | 制造商:Xilinx 功能描述: |

| XC95288XVSERIES | 制造商:XILINX 制造商全稱:XILINX 功能描述:High-Performance CPLD |

| XC9536 | 制造商:XILINX 制造商全稱:XILINX 功能描述:XC9536 In-System Programmable CPLD |

| XC9536-10 | 制造商:XILINX 制造商全稱:XILINX 功能描述:XC9536 In-System Programmable CPLD |

| XC9536-10CS48C | 功能描述:IC CPLD 36 MCELL C-TEMP 48-CSP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - CPLD(復雜可編程邏輯器件) 系列:XC9500 標準包裝:24 系列:CoolRunner II 可編程類型:系統(tǒng)內(nèi)可編程 最大延遲時間 tpd(1):7.1ns 電壓電源 - 內(nèi)部:1.7 V ~ 1.9 V 邏輯元件/邏輯塊數(shù)目:24 宏單元數(shù):384 門數(shù):9000 輸入/輸出數(shù):173 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:208-BFQFP 供應商設備封裝:208-PQFP(28x28) 包裝:托盤 |

發(fā)布緊急采購,3分鐘左右您將得到回復。