- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄19485 > XCR3064XL-7VQ100I (Xilinx Inc)IC CPLD 64 MACROCELL HP 100-VQFP PDF資料下載

參數(shù)資料

| 型號(hào): | XCR3064XL-7VQ100I |

| 廠商: | Xilinx Inc |

| 文件頁(yè)數(shù): | 12/12頁(yè) |

| 文件大小: | 0K |

| 描述: | IC CPLD 64 MACROCELL HP 100-VQFP |

| 標(biāo)準(zhǔn)包裝: | 90 |

| 系列: | CoolRunner XPLA3 |

| 可編程類(lèi)型: | 系統(tǒng)內(nèi)可編程(最少 1K 次編程/擦除循環(huán)) |

| 最大延遲時(shí)間 tpd(1): | 7.0ns |

| 電壓電源 - 內(nèi)部: | 2.7 V ~ 3.6 V |

| 邏輯元件/邏輯塊數(shù)目: | 4 |

| 宏單元數(shù): | 64 |

| 門(mén)數(shù): | 1500 |

| 輸入/輸出數(shù): | 68 |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類(lèi)型: | 表面貼裝 |

| 封裝/外殼: | 100-TQFP |

| 供應(yīng)商設(shè)備封裝: | 100-VQFP(14x14) |

| 包裝: | 托盤(pán) |

CoolRunner XPLA3 CPLD

DS012 (v2.5) May 26, 2009

Product Specification

R

JTAG and ISP Interfacing

A number of industry-established methods exist for

JTAG/ISP interfacing with CPLDs and other integrated cir-

cuits. The CoolRunner XPLA3 family supports the following

methods:

Xilinx HW 130

PC Parallel Port

Workstation or PC Serial Port

Embedded Processor

Automated Test Equipment

Third Party Programmers

Xilinx ISP Programming Tools

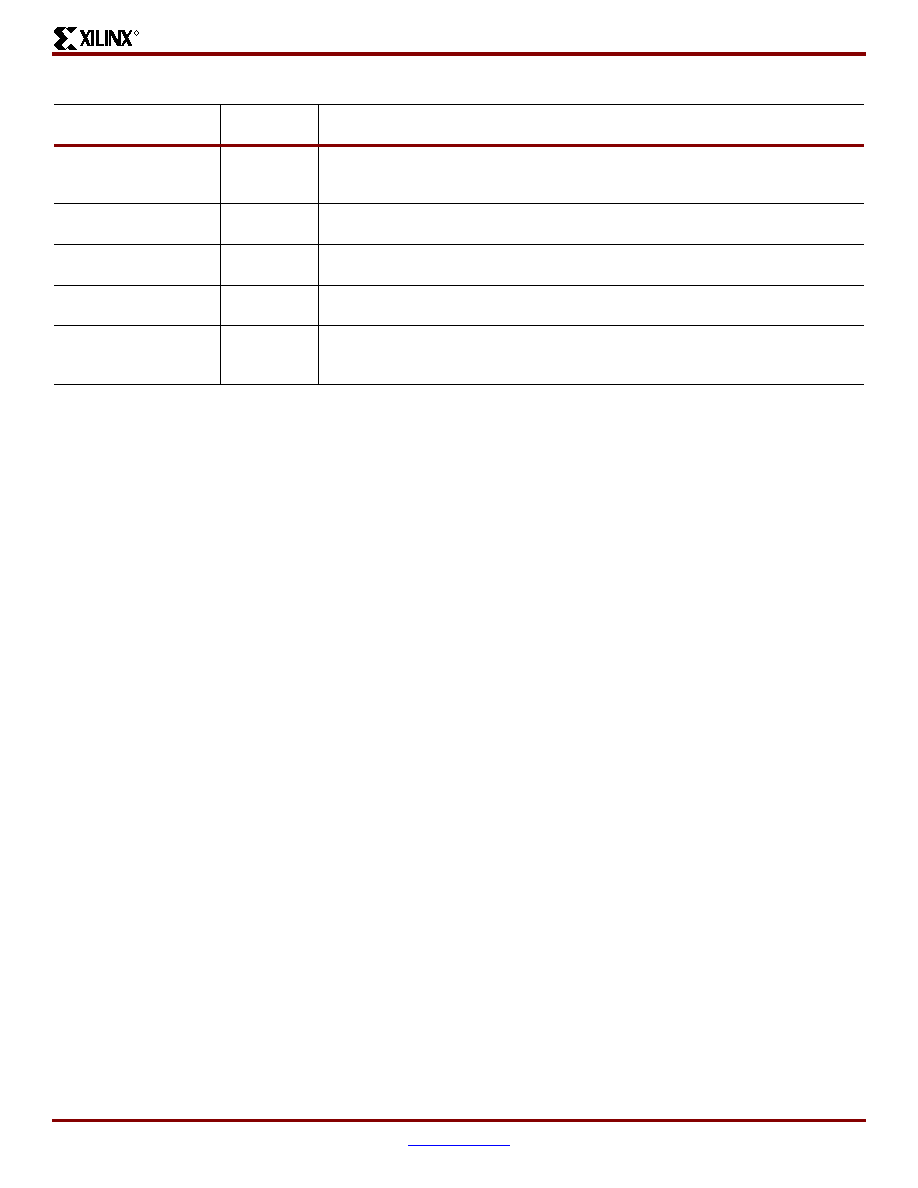

Table 6: Low-level ISP Commands

Instruction

(Register Used)

Instruction

Code

Description

Enable

(ISP Shift Register)

01001

Enables the Erase, Program, and Verify commands. Using the Enable instruction

before the Erase, Program, and Verify instructions allows the user to specify the

outputs of the device using the JTAG Boundary-Scan Sample/Preload command.

Erase

(ISP Shift Register)

01010

Erases the entire EEPROM array. User can define the outputs during this

operation by using the JTAG Sample/Preload command.

Program

(ISP Shift Register)

01011

Programs the data in the ISP Shift Register into the addressed EEPROM row. The

outputs can be defined by using the JTAG Sample/Preload command.

Disable

(ISP Shift Register)

10000

Allows the user to leave ISP mode. It selects the ISP register to be directly

connected between TDO and TDI.

Verify

(ISP Shift Register)

01100

Transfers the data from the addressed row to the ISP Shift Register. The data can

then be shifted out and compared with the JEDEC file. The user can define the

outputs during this operation.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TPSC155M050R1500 | CAP TANT 1.5UF 50V 20% 2312 |

| MAX6646MUA+T | IC SENSOR REMOTE SMBUS 8UMAX |

| ADSP-BF522BBCZ-4A | IC DSP CTRLR 400MHZ 208CSPBGA |

| TPSC155K050R1500 | CAP TANT 1.5UF 50V 10% 2312 |

| ADSP-BF536BBCZ-3A | IC DSP CTLR 16BIT 182CSPBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XCR3064XL-7VQ44C | 功能描述:IC CPLD 64 MACROCELL HP 44-VQFP RoHS:否 類(lèi)別:集成電路 (IC) >> 嵌入式 - CPLD(復(fù)雜可編程邏輯器件) 系列:CoolRunner XPLA3 標(biāo)準(zhǔn)包裝:24 系列:CoolRunner II 可編程類(lèi)型:系統(tǒng)內(nèi)可編程 最大延遲時(shí)間 tpd(1):7.1ns 電壓電源 - 內(nèi)部:1.7 V ~ 1.9 V 邏輯元件/邏輯塊數(shù)目:24 宏單元數(shù):384 門(mén)數(shù):9000 輸入/輸出數(shù):173 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:208-BFQFP 供應(yīng)商設(shè)備封裝:208-PQFP(28x28) 包裝:托盤(pán) |

| XCR3064XL-7VQ44I | 功能描述:IC CPLD 64 MACROCELL HP 44-VQFP RoHS:否 類(lèi)別:集成電路 (IC) >> 嵌入式 - CPLD(復(fù)雜可編程邏輯器件) 系列:CoolRunner XPLA3 標(biāo)準(zhǔn)包裝:24 系列:CoolRunner II 可編程類(lèi)型:系統(tǒng)內(nèi)可編程 最大延遲時(shí)間 tpd(1):7.1ns 電壓電源 - 內(nèi)部:1.7 V ~ 1.9 V 邏輯元件/邏輯塊數(shù)目:24 宏單元數(shù):384 門(mén)數(shù):9000 輸入/輸出數(shù):173 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:208-BFQFP 供應(yīng)商設(shè)備封裝:208-PQFP(28x28) 包裝:托盤(pán) |

| XCR3064XL-7VQG100C | 制造商:Xilinx 功能描述:CPLD COOLRUNNER XPLA3 1.5K GATES 64 MCRCLLS 166.67MHZ 0.35UM - Trays |

| XCR3064XL-7VQG100I | 制造商:Xilinx 功能描述:XLXXCR3064XL-7VQG100I IC SYSTEM GATE 制造商:Xilinx 功能描述:CPLD COOLRUNNER XPLA3 1.5K GATES 64 MCRCLLS 166.67MHZ 0.35UM - Trays |

| XCR3064XL-7VQG44C | 制造商:Xilinx 功能描述:XLXXCR3064XL-7VQG44C IC SYSTEM GATE 制造商:Xilinx 功能描述:CPLD COOLRUNNER XPLA3 1.5K GATES 64 MCRCLLS 166.67MHZ 0.35UM - Trays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。