- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄4139 > XCS40XL-5PQ240C (Xilinx Inc)IC FPGA 3.3V C-TEMP 240-PQFP PDF資料下載

參數(shù)資料

| 型號(hào): | XCS40XL-5PQ240C |

| 廠商: | Xilinx Inc |

| 文件頁(yè)數(shù): | 3/83頁(yè) |

| 文件大小: | 0K |

| 描述: | IC FPGA 3.3V C-TEMP 240-PQFP |

| 產(chǎn)品變化通告: | Product Discontinuation 26/Oct/2011 |

| 標(biāo)準(zhǔn)包裝: | 24 |

| 系列: | Spartan®-XL |

| LAB/CLB數(shù): | 784 |

| 邏輯元件/單元數(shù): | 1862 |

| RAM 位總計(jì): | 25088 |

| 輸入/輸出數(shù): | 192 |

| 門(mén)數(shù): | 40000 |

| 電源電壓: | 3 V ~ 3.6 V |

| 安裝類(lèi)型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 240-BFQFP |

| 供應(yīng)商設(shè)備封裝: | 240-PQFP(32x32) |

第1頁(yè)第2頁(yè)當(dāng)前第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)

Spartan and Spartan-XL FPGA Families Data Sheet

DS060 (v2.0) March 1, 2013

Product Specification

R

Product Obsolete/Under Obsolescence

CLB Interface

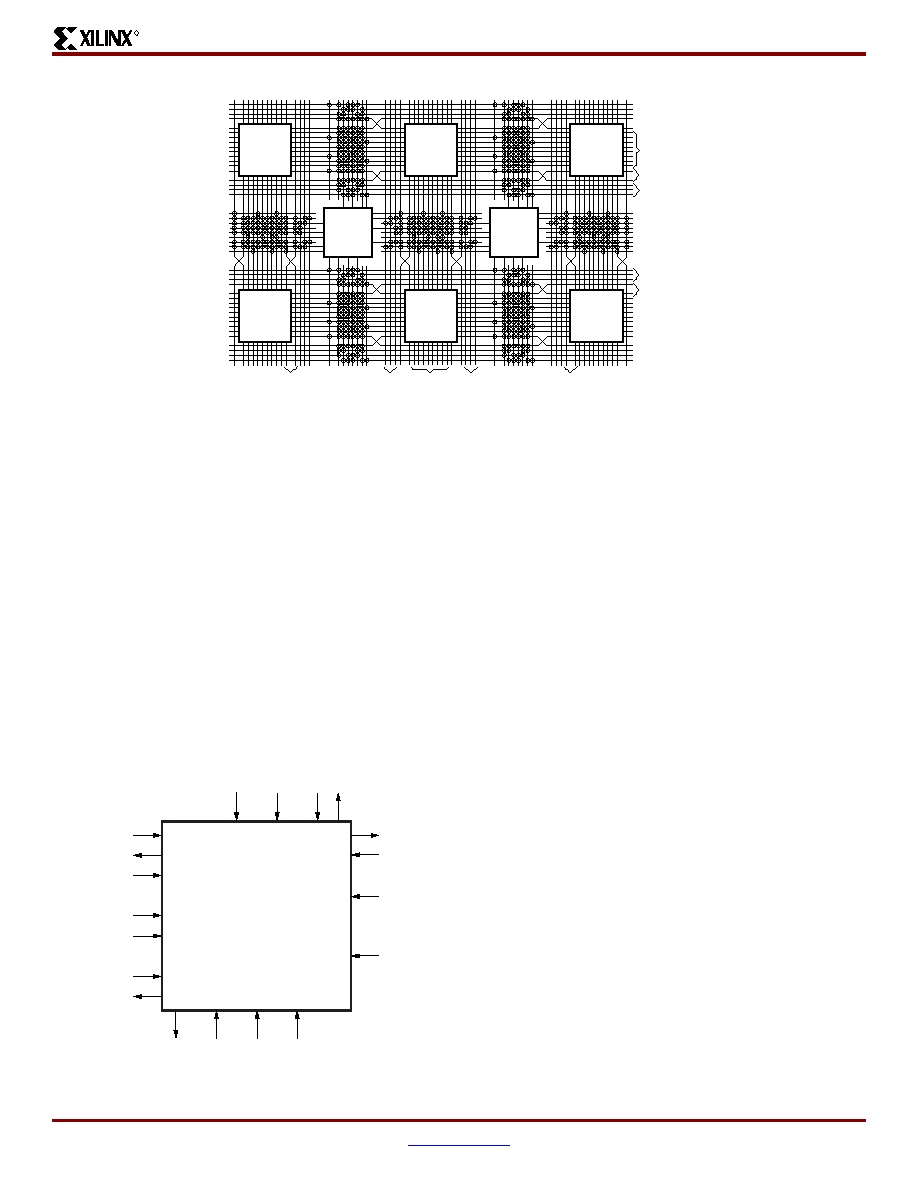

A block diagram of the CLB interface signals is shown in

Figure 9. The input signals to the CLB are distributed evenly

on all four sides providing maximum routing flexibility. In

general, the entire architecture is symmetrical and regular.

It is well suited to established placement and routing algo-

rithms. Inputs, outputs, and function generators can freely

swap positions within a CLB to avoid routing congestion

during the placement and routing operation. The exceptions

are the clock (K) input and CIN/COUT signals. The K input

is routed to dedicated global vertical lines as well as four

single-length lines and is on the left side of the CLB. The

CIN/COUT signals are routed through dedicated intercon-

nects which do not interfere with the general routing struc-

ture. The output signals from the CLB are available to drive

both vertical and horizontal channels.

Programmable Switch Matrices

The horizontal and vertical single- and double-length lines

intersect at a box called a programmable switch matrix

(PSM). Each PSM consists of programmable pass transis-

tors used to establish connections between the lines (see

For example, a single-length signal entering on the right

side of the switch matrix can be routed to a single-length

line on the top, left, or bottom sides, or any combination

thereof, if multiple branches are required. Similarly, a dou-

ble-length signal can be routed to a double-length line on

any or all of the other three edges of the programmable

switch matrix.

Single-Length Lines

Single-length lines provide the greatest interconnect flexibil-

ity and offer fast routing between adjacent blocks. There are

eight vertical and eight horizontal single-length lines associ-

ated with each CLB. These lines connect the switching

matrices that are located in every row and column of CLBs.

Single-length lines are connected by way of the program-

mable switch matrices, as shown in Figure 10. Routing con-

nectivity is shown in Figure 8.

Single-length lines incur a delay whenever they go through

a PSM. Therefore, they are not suitable for routing signals

for long distances. They are normally used to conduct sig-

nals within a localized area and to provide the branching for

nets with fanout greater than one.

Figure 8: Spartan/XL CLB Routing Channels and Interface Block Diagram

PSM

CLB

PSM

8 Singles

2 Doubles

3 Longs

2 Doubles

3 Longs

2 Doubles

8 Singles

DS060_09_041901

Figure 9: CLB Interconnect Signals

CIN

Y

G3

C3

F3

COUT

G1

C1

K

F1

X

XQ

F4

C4

G4

YQ

F2

C2

G2

CLB

DS060_08_081100

Rev 1.1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XCS40XL-5PQ208C | IC FPGA 3.3V C-TEMP 208-PQFP |

| IDT71V35761S166BG | IC SRAM 4MBIT 166MHZ 119BGA |

| IDT71V3556SA166BG | IC SRAM 4MBIT 166MHZ 119BGA |

| IDT71V25761S200BG | IC SRAM 4MBIT 200MHZ 119BGA |

| IDT71V25761S183BG | IC SRAM 4MBIT 183MHZ 119BGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XCS40XL-5PQ240I | 制造商:XILINX 制造商全稱(chēng):XILINX 功能描述:Spartan and Spartan-XL FPGA |

| XCS40XL-5PQ256C | 制造商:XILINX 制造商全稱(chēng):XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS40XL-5PQ256I | 制造商:XILINX 制造商全稱(chēng):XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS40XL-5PQ280C | 制造商:XILINX 制造商全稱(chēng):XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS40XL-5PQ280I | 制造商:XILINX 制造商全稱(chēng):XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。