- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372925 > XPC855TZP50 Controller Miscellaneous - Datasheet Reference PDF資料下載

參數(shù)資料

| 型號: | XPC855TZP50 |

| 英文描述: | Controller Miscellaneous - Datasheet Reference |

| 中文描述: | 控制器雜項-數(shù)據(jù)表參考 |

| 文件頁數(shù): | 35/76頁 |

| 文件大小: | 825K |

| 代理商: | XPC855TZP50 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁當(dāng)前第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁

MOTOROLA

MPC850 (Rev. A/B/C) Hardware Specifications

35

Layout Practices

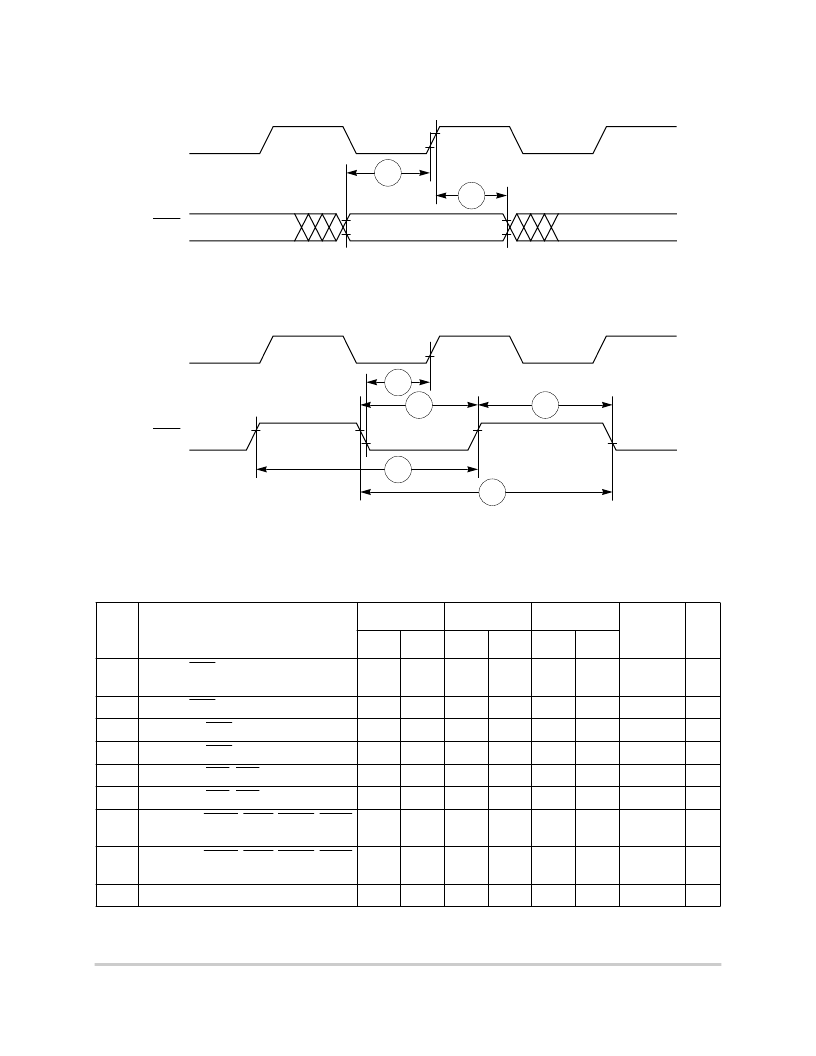

Figure 6-22 provides the interrupt detection timing for the external level-sensitive lines.

Figure 6-22. Interrupt Detection Timing for External Level Sensitive Lines

Figure 6-23 provides the interrupt detection timing for the external edge-sensitive lines.

Figure 6-23. Interrupt Detection Timing for External Edge Sensitive Lines

Table 6-8 shows the PCMCIA timing for the MPC850.

Table 6-8. PCMCIA Timing

Num

Characteristic

50MHz

66MHz

80 MHz

FFACTOR

Unit

Min

Max

Min

Max

Min

Max

P44

A[6–31], REG valid to PCMCIA strobe

asserted.

1

13.00

—

21.00

—

17.00

—

0.750

ns

P45

A[6–31], REG valid to ALE negation.

1

18.00

—

28.00

—

23.00

—

1.000

ns

P46

CLKOUT to REG valid

5.00

13.00

8.00

16.00

6.00

14.00

0.250

ns

P47

CLKOUT to REG Invalid.

6.00

—

9.00

—

7.00

—

0.250

ns

P48

CLKOUT to CE1, CE2 asserted.

5.00

13.00

8.00

16.00

6.00

14.00

0.250

P49

CLKOUT to CE1, CE2 negated.

5.00

13.00

8.00

16.00

6.00

14.00

0.250

ns

P50

CLKOUT to PCOE, IORD, PCWE, IOWR

assert time.

—

11.00

—

11.00

—

11.00

—

ns

P51

CLKOUT to PCOE, IORD, PCWE, IOWR

negate time.

2.00

11.00

2.00

11.00

2.00

11.00

—

ns

P52

CLKOUT to ALE assert time

5.00

13.00

8.00

16.00

6.00

14.00

0.250

ns

CLKOUT

IRQx

I39

I40

CLKOUT

IRQx

I39

I41

I42

I43

I43

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XPC850CZT50BU | Microprocessor |

| XPC850CZT66BU | Microprocessor |

| XPC850DECZT50BU | Microprocessor |

| XPC850DECZT66BU | Microprocessor |

| XPC850DEZT50BU | Microprocessor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XPC855TZP50D4 | 制造商:Motorola Inc 功能描述: |

| XPC855TZP66D4 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Family Hardware Specifications |

| XPC855TZP80 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Controller Miscellaneous - Datasheet Reference |

| XPC855TZP80D4 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Family Hardware Specifications |

| XPC857DSLZP50B | 制造商:Freescale Semiconductor 功能描述: 制造商:Freescale Semiconductor 功能描述:MPU MPC8XX RISC 32BIT 0.32UM 50MHZ 357BGA - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。