- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372930 > XQR4036XL-3CB228M Field Programmable Gate Array (FPGA) PDF資料下載

參數(shù)資料

| 型號: | XQR4036XL-3CB228M |

| 英文描述: | Field Programmable Gate Array (FPGA) |

| 中文描述: | 現(xiàn)場可編程門陣列(FPGA) |

| 文件頁數(shù): | 15/20頁 |

| 文件大小: | 201K |

| 代理商: | XQR4036XL-3CB228M |

QPRO XQR4000XL Radiation Hardened FPGAs

DS071 (v1.1) June 25, 2000

Product Specification

This Material Copyrighted by Its Respective Manufacturer

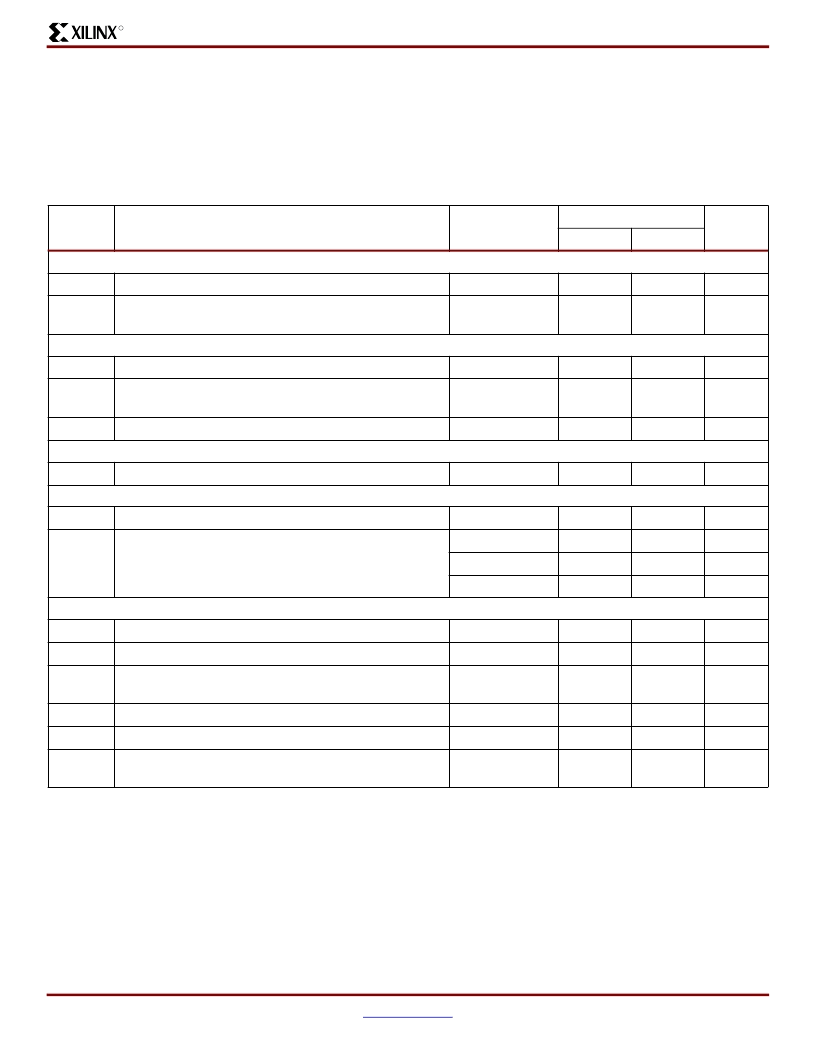

1-800-255-7778XQR4000XL IOB Input Switching Characteristic Guidelines

Testing of switching parameters is modeled after testing

methods specified by MIL-M-38510/605. All devices are

100% functionally tested. Internal timing parameters are

derived from measuring internal test patterns. Listed below

are representative values. For more specific, more precise,

and worst-case guaranteed data, use the values reported

by the static timing analyzer (TRCE in the Xilinx Develop-

ment System) and back-annotated to the simulation netlist.

These path delays, provided as a guideline, have been

extracted from the static timing analyzer report. All timing

parameters assume worst-case operating conditions (sup-

ply voltage and junction temperature)

.

Symbol

Description

Device

-3

Units

Min

Max

Clocks

T

ECIK

T

OKIK

Clock enable (EC) to clock (IK)

All devices

0.1

-

ns

Delay from FCL enable (OK) active edge to IFF clock

(IK) active edge

All devices

2.2

-

ns

Setup Times

T

PICK

T

PICKF

Pad to clock (IK), no delay

All devices

1.7

-

ns

Pad to clock (IK), via transparent fast capture latch, no

delay

All devices

2.3

-

ns

T

POCK

Hold Times

Pad to fast capture latch enable (OK), no delay

All devices

1.2

-

ns

All Hold Times

All devices

0

-

ns

Global Set/Reset

T

MRW

T

RRI

Minimum GSR pulse width

Delay from GSR input to any Q

(2)

All devices

-

19.8

ns

XQR4013XL

-

15.9

ns

XQR4036XL

-

22.5

ns

XQR4062XL

-

29.1

ns

Propagation Delays

T

PID

T

PLI

T

PFLI

Pad to I1, I2

All devices

-

1.6

ns

Pad to I1, I2 via transparent input latch, no delay

All devices

-

3.1

ns

Pad to I1, I2 via transparent FCL and input latch, no

delay

All devices

-

3.7

ns

T

IKRI

T

IKLI

T

OKLI

Clock (IK) to I1, I2 (flip-flop)

All devices

-

1.7

ns

Clock (IK) to I1, I2 (latch enable, active Low)

All devices

-

1.8

ns

FCL enable (OK) active edge to I1, I2

(via transparent standard input latch)

All devices

-

3.6

ns

Notes:

1.

2.

IFF = Input Flip-Flop or Latch, FCL = Fast Capture Latch

Indicates Minimum Amount of Time to Assure Valid Data.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XQR4062XL-3CB228M | Field Programmable Gate Array (FPGA) |

| XR-082CP | Voltage-Feedback Operational Amplifier |

| XR-082M | Voltage-Feedback Operational Amplifier |

| XR-082N | Voltage-Feedback Operational Amplifier |

| XR-084CP | Voltage-Feedback Operational Amplifier |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XQS14+A2FZ | 制造商:Panasonic Industrial Company 功能描述:SCREW (1/10) |

| XQS2+A5FZ | 制造商:Panasonic Industrial Company 功能描述:SCREW |

| XQS2+AJ8FZ | 制造商:Panasonic Industrial Company 功能描述:SCREW |

| XQT2LMR11D | 制造商:SunLED Group 功能描述: |

| XQT2LUG11D | 制造商:SunLED Group 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。