- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16492 > XR16V564DIV-0A-EB (Exar Corporation)EVAL BOARD FOR XR16V564D 64LQFP PDF資料下載

參數(shù)資料

| 型號: | XR16V564DIV-0A-EB |

| 廠商: | Exar Corporation |

| 文件頁數(shù): | 26/54頁 |

| 文件大?。?/td> | 0K |

| 描述: | EVAL BOARD FOR XR16V564D 64LQFP |

| 標準包裝: | 1 |

| 系列: | * |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁

XR16V564/564D

32

2.25V TO 3.6V QUAD UART WITH 32-BYTE FIFO

REV. 1.0.4

LCR[5]: TX and RX Parity Select

If the parity bit is enabled, LCR BIT-5 selects the forced parity format.

LCR BIT-5 = LOW, parity is not forced (default).

LCR BIT-5 = HIGH and LCR BIT-4 = LOW, parity bit is forced to a logical 1 for the transmit and receive data.

LCR BIT-5 = HIGH and LCR BIT-4 = LOW, parity bit is forced to a logical 0 for the transmit and receive data.

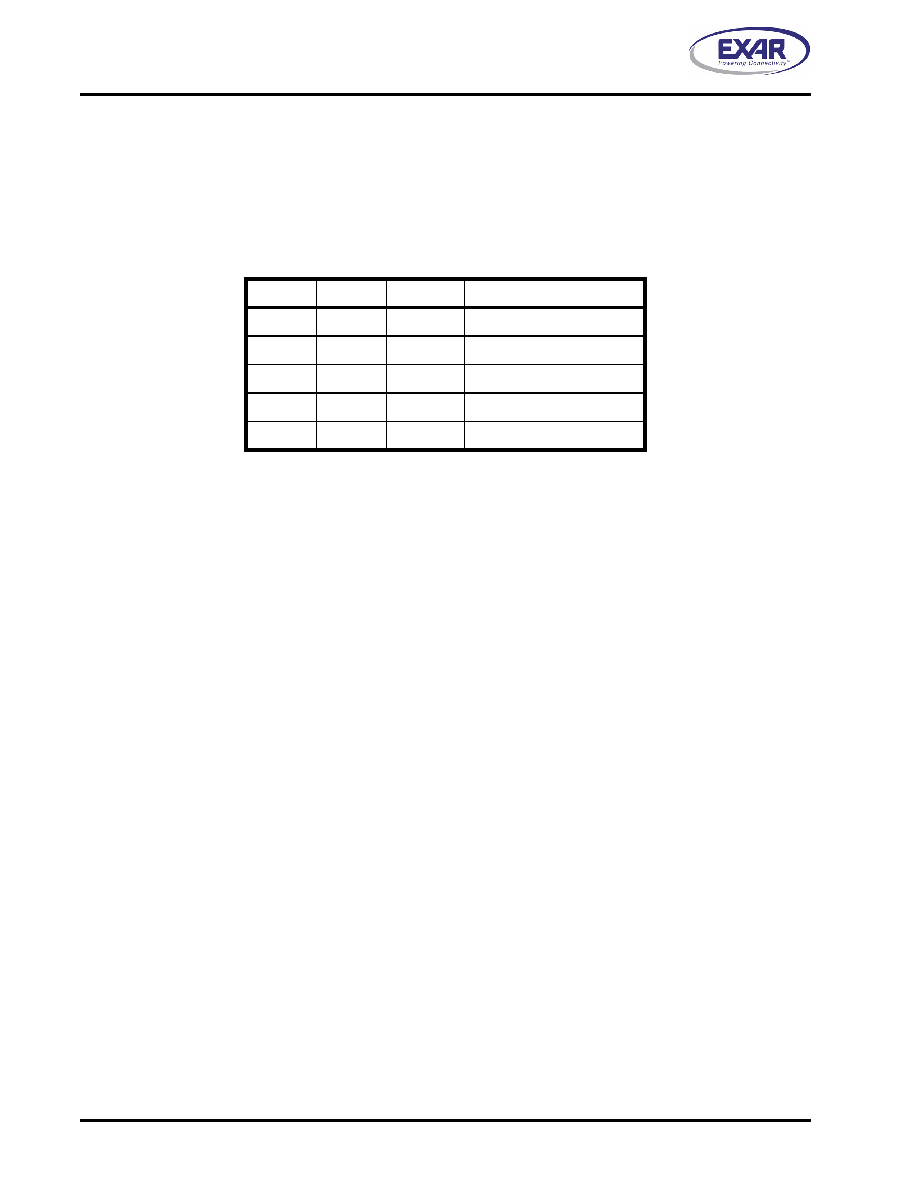

TABLE 13: PARITY SELECTION

LCR BIT-5 LCR BIT-4 LCR BIT-3

PARITY SELECTION

X

0

No parity

0

1

Odd parity

0

1

Even parity

1

0

1

Force parity to mark, HIGH

1

Forced parity to space, LOW

LCR[6]: Transmit Break Enable

When enabled, the Break control bit causes a break condition to be transmitted (the TX output is forced to a

“space’, LOW, state). This condition remains, until disabled by setting LCR bit-6 to a logic 0.

Logic 0 = No TX break condition. (default)

Logic 1 = Forces the transmitter output (TX) to a “space”, LOW, for alerting the remote receiver of a line

break condition.

LCR[7]: Baud Rate Divisors Enable

Baud rate generator divisor (DLL/DLM/DLD) enable.

Logic 0 = Data registers are selected (default).

Logic 1 = Divisor latch registers are selected.

4.7

Modem Control Register (MCR) or General Purpose Outputs Control - Read/Write

The MCR register is used for controlling the serial/modem interface signals or general purpose inputs/outputs.

MCR[0]: DTR# Output

The DTR# pin is a modem control output. If the modem interface is not used, this output may be used as a

general purpose output.

Logic 0 = Force DTR# output HIGH (default).

Logic 1 = Force DTR# output LOW.

MCR[1]: RTS# Output

The RTS# pin is a modem control output and may be used for automatic hardware flow control by enabled by

EFR bit-6. If the modem interface is not used, this output may be used as a general purpose output.

Logic 0 = Force RTS# output HIGH (default).

Logic 1 = Force RTS# output LOW.

MCR[2]: Reserved

OP1# is not available as an output pin on the V564. But it is available for use during Internal Loopback Mode.

In the Loopback Mode, this bit is used to write the state of the modem RI# interface signal.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M3BBK-1618R | IDC CABLE - MSR16K/MC16M/MSR16K |

| CDRH2D14NP-1R5NC | INDUCTOR POWER 1.5UH 2A SMD |

| RPP30-2424SW-F | CONV DC/DC 30W 9-36VIN 24VOUT |

| XC61CN2202MR-G | IC SUPERVISOR 2.2V SOT23-3 |

| 6374039-8 | C/A 62.5/125, PLNM ZIP, SC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XR16V564DIV-F | 功能描述:UART 接口集成電路 UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR16V564DIVTR-F | 制造商:Exar Corporation 功能描述:UART 4-CH 32Byte FIFO 2.5V/3.3V 64-Pin LQFP T/R 制造商:Exar Corporation 功能描述:XR16V564DIVTR-F |

| XR16V564IJ | 制造商:Rochester Electronics LLC 功能描述: 制造商:Exar Corporation 功能描述: |

| XR16V564IJ-0A-EVB | 功能描述:UART 接口集成電路 Supports V564 68 ld PLCC, ISA Interface RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR16V564IJ-F | 功能描述:UART 接口集成電路 UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。