- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄8746 > XRD54L10AIDTR-F (Exar Corporation)IC DAC 10BIT SRL LP 8SOIC PDF資料下載

參數(shù)資料

| 型號: | XRD54L10AIDTR-F |

| 廠商: | Exar Corporation |

| 文件頁數(shù): | 16/16頁 |

| 文件大小: | 0K |

| 描述: | IC DAC 10BIT SRL LP 8SOIC |

| 標準包裝: | 2,500 |

| 設置時間: | 13µs |

| 位數(shù): | 10 |

| 數(shù)據(jù)接口: | 串行 |

| 轉(zhuǎn)換器數(shù)目: | 1 |

| 電壓電源: | 單電源 |

| 功率耗散(最大): | 155mW |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 8-SOIC(0.154",3.90mm 寬) |

| 供應商設備封裝: | 8-SOIC |

| 包裝: | 帶卷 (TR) |

| 輸出數(shù)目和類型: | * |

| 采樣率(每秒): | * |

XRD54L08/L10/L12

9

Rev. 1.30

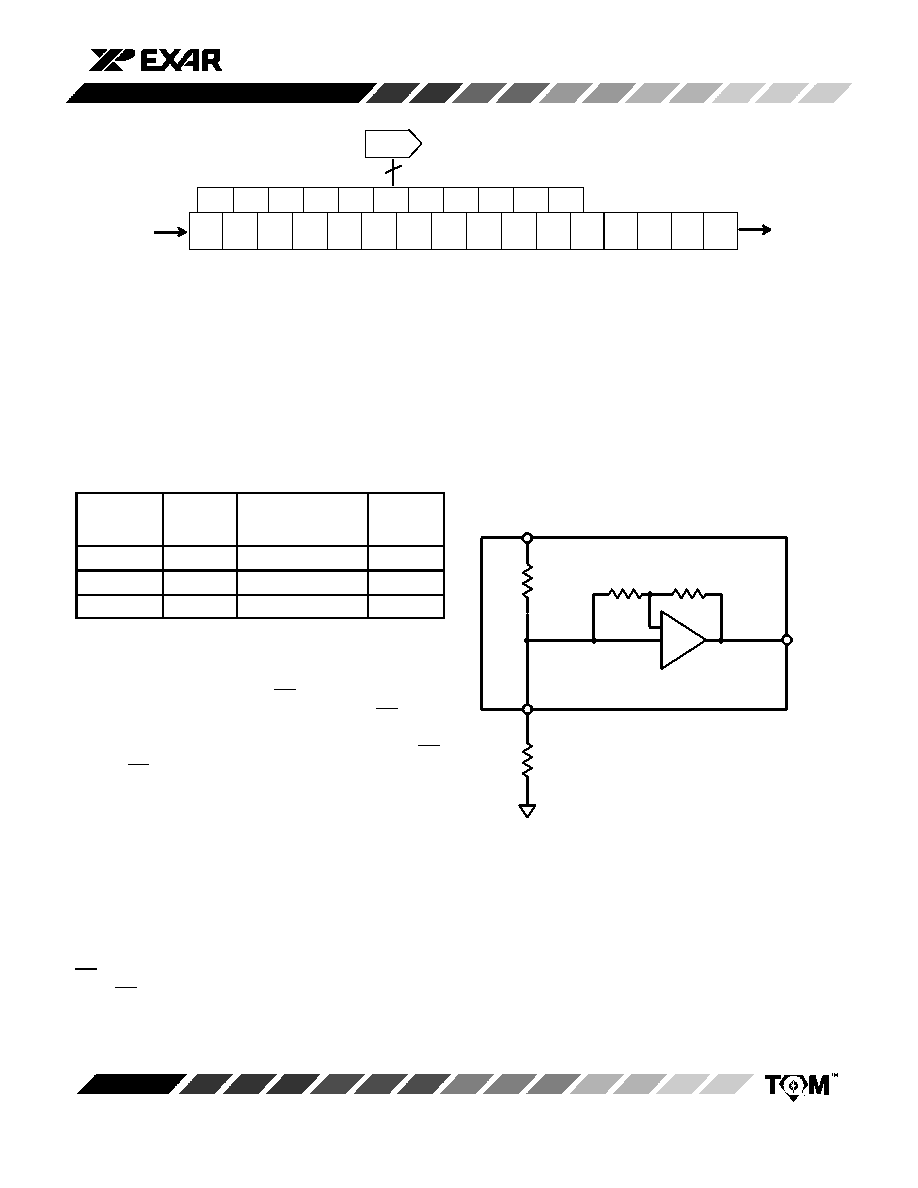

Figure 6. Shift Register Format

DOUT

SDIN

X

DAC

MSB

n

The DACs are programmed by a 16 bit word of serial data.

The format of the serial input register is shown in Figure 6.

The leading 4 bits are not used to update the DAC. If the

DAC is not daisy-chained then only a 12 bit serial word is

needed to program the DAC. The next 8, 10 or 12 bits

after the 4 leading bits are data bits. The XRD54L08’s first

8 bits are valid data and the trailing 4 bits must be set to 0.

Figure 7 demonstrates the 16 bit digital word for the 8,

10,12 bit DACs.

Part

Leading

Unused

Bits

Data Bits

MSB

LSB

Trailing

“0”

Bits

XRD54L12

XXXX

XXXXXXXX

None

XRD54L10

XXXX

XXXXXXXX

00

XRD54L08

XXXX

XXXXXXXX

0000

Table 2. 16-Bit Digital Word Register for XRD54L08,

XRD54L10, XRD54L12.

SCLK should be held low when CS transitions low. Data is

clocked in on the rising edge of SCLK when CS is low.

SDIN data is held in a 16 bit serial shift register. The DAC

is updated with the data bits on the rising edge of CS.

When CS is high data is not shifted into the

XRD54L08/L10/L12.

Daisy-Chaining

The digital output port (DOUT) has a 4mA drive for greater

fan-out capability when daisy-chaining. DOUT allows

cascading of multiple DACs with the same serial data

stream. The data at SDIN appears at DOUT after 16 clock

cycles plus one clock width (tCH) and a propagation delay

(tDO). DOUT remains in the state of the last data bit when

CS is high. DOUT changes on the falling edge of SCLK

when CS is low.

Any number of DACs can be connected in this way by

connecting DOUT of one DAC to SDIN of the next DAC.

ACFT Feedthrough (DAC Code = 0)

AC Feedthrough from VREFIN to VOUT is minimized with

low impedance grounding as shown in

Figure 7. If the

DAC data is set to all “0”s then VOUT is a function of the

divider between the DAC string impedance and ground

impedance. See the Power Supply and Grounding

section for recommendations.

The typical AC

feedthrough for a 1kHz 2Vpp signal with code = 0 is

-80dB.

Figure 7. ACFT Feedthrough Equivalent

Circuit, DAC Code =0

VREFIN

XRD54L08/L10/L12

VOUT

GND

RGND

Analog GND

RIN

--

+

Compatible with MAX515 & MAX539

The XRD54L08/L10/L12 family of DACs are functionally

campatible with the MAX515 & MAX539 while providing

significant improvements.

The XRD54L08/L10/L12

DACs have lower power, faster serial ports, and a

constant reference impedance to minimize the reference

driving requirements and maximize system linearity while

相關PDF資料 |

PDF描述 |

|---|---|

| MC100EP14DTG | IC CLK BUFF MUX 2:5 2GHZ 20TSSOP |

| MC100LVEP111FAG | IC CLK BUFF MUX 2:10 3GHZ 32LQFP |

| LTC2621CDD-1#TRPBF | IC DAC 12BIT SGL R-R VOUT 10DFN |

| NB6L611MNG | IC CLOCK BUFFER 1:2 4GHZ 16-QFN |

| LTC2621CDD#TRPBF | IC DAC 12BIT SGL R-R VOUT 10DFN |

相關代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRD54L10AIP | 制造商:EXAR 制造商全稱:EXAR 功能描述:3V Low Power Voltage Output Serial 8/10/12-Bit DAC Family |

| XRD54L10AIP-F | 功能描述:數(shù)模轉(zhuǎn)換器- DAC RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉(zhuǎn)換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時間:1 us 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| XRD54L12AID | 制造商:EXAR 制造商全稱:EXAR 功能描述:3V Low Power Voltage Output Serial 8/10/12-Bit DAC Family |

| XRD54L12AID-F | 功能描述:數(shù)模轉(zhuǎn)換器- DAC RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉(zhuǎn)換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時間:1 us 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| XRD54L12AIDTR-F | 功能描述:數(shù)模轉(zhuǎn)換器- DAC RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉(zhuǎn)換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時間:1 us 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復。