- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373766 > Z86307 (ZiLOG, Inc.) 8 Bit CMOS MCU for PS/2 mouse(8位CMOS鼠標微控制器) PDF資料下載

參數(shù)資料

| 型號: | Z86307 |

| 廠商: | ZiLOG, Inc. |

| 英文描述: | 8 Bit CMOS MCU for PS/2 mouse(8位CMOS鼠標微控制器) |

| 中文描述: | 8位CMOS微控制器的PS / 2鼠標(8位的CMOS鼠標微控制器) |

| 文件頁數(shù): | 17/24頁 |

| 文件大小: | 326K |

| 代理商: | Z86307 |

Z86307

8-Bit CMOS Z8 MCU For PS/2 Mouse and Trackball Applications

ZiLOG

17

P R E L I M I N A R Y

DS007400-PER0399

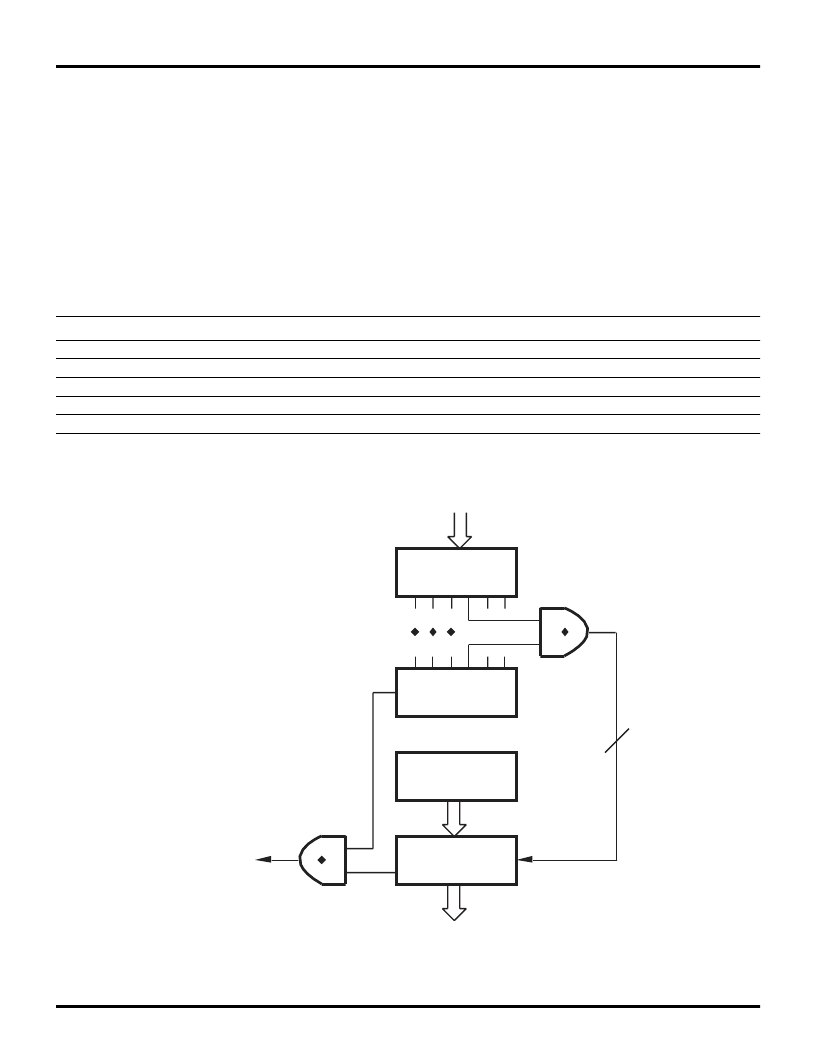

Interrupts.

The Z86307 features four interrupts from four

different sources. These interrupts are maskable and prior-

itized (Figure 19). The four sources are divided as follows:

the falling edge of P31, P33, and the two counter/timers.

The Interrupt Mask Register globally or individually en-

ables or disables the four interrupt requests (Table 4).

When more than one interrupt is pending, priorities are re-

solved by a programmable priority encoder that is con-

trolled by the Interrupt Priority register. All Z86307 inter-

rupts are vectored through locations in program memory.

When an interrupt machine cycle is activated, an interrupt

request is granted. This disables all subsequent interrupts,

saves the Program Counter and Status Flags, and then

branches to the program memory vector location reserved

for that interrupt. This memory location and the next byte

contain the 16-bit starting address of the Interrupt Service

Routine for that particular interrupt request.

To accommodate polled interrupt systems, interrupt inputs

are masked and the Interrupt Request Register is polled to

determine which of the interrupt requests needs service.

Table 4. Interrupt Types, Sources, and Vectors

Source

P33

P31

T0

T1

Name

IRQ1

IRQ2

IRQ4

IRQ5

Vector

2,3

4,5

8,9

10,11

Location

External

External

Internal

Internal

Comments

Falling Edge

Falling Edge

Note:

IRQ0 and IRQ2 are disabled.

Figure 19. Interrupt Block Diagram

IRQ

IMR

IPR

Priority

Logic

6

Vector Select

Global

Interrupt

Enable

Interrupt

Request

IRQ0–IRQ5

相關PDF資料 |

PDF描述 |

|---|---|

| Z86317 | CMOS Z8 8-BIT MICROCONTROLLER |

| Z86418 | Z8 8-BIT Mouse Controller(8位CMOS鼠標微控制器) |

| Z86733 | 1.0UF/630VDC METAL POLY CAP |

| Z86743 | CMOS Z8 OTP Microcontroller(CMOS Z8系列一次可編程微控制器) |

| Z86E33 | CMOS Z8 OTP Microcontroller(CMOS Z8系列一次可編程微控制器) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| Z8630804PSC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| Z8630804SSC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| Z86317 | 制造商:ZILOG 制造商全稱:ZILOG 功能描述:CMOS Z8 8-BIT MICROCONTROLLER |

| Z8631704PSC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| Z8631704SSC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復。