- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373767 > Z86C8316VSC (ZILOG INC) Z8 MCU MICROCONTROLLERS PDF資料下載

參數(shù)資料

| 型號: | Z86C8316VSC |

| 廠商: | ZILOG INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | Z8 MCU MICROCONTROLLERS |

| 中文描述: | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQCC28 |

| 封裝: | PLASTIC, LCC-28 |

| 文件頁數(shù): | 34/46頁 |

| 文件大小: | 957K |

| 代理商: | Z86C8316VSC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁當(dāng)前第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁

Z86C83/C84

Z8

MCU Microcontrollers

34

DS96DZ80203

In order to enter STOP (or HALT) mode, it is necessary to

first flush the instruction pipeline to avoid suspending

execution in mid-instruction. To do this, the user must

execute a NOP (opcode = FFH) immediately before the

appropriate sleep instruction, that is,

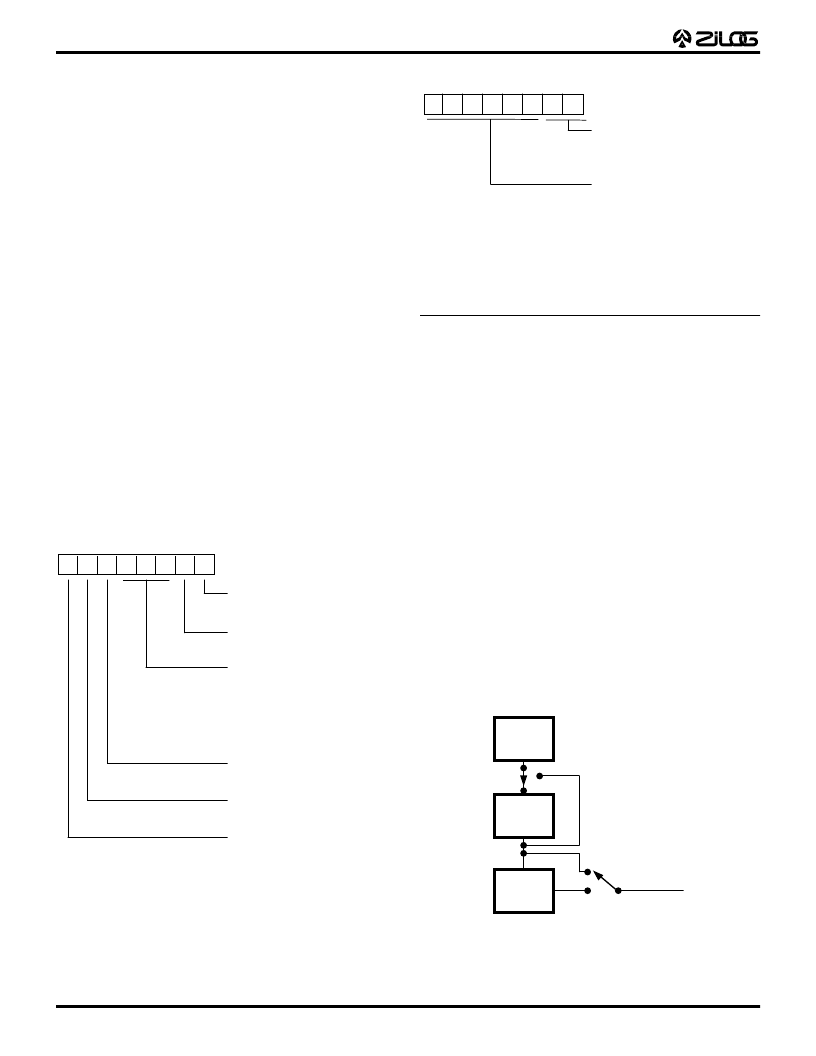

STOP-Mode Recovery (SMR) Register.

This register se-

lects the clock divide value and determines the mode of

STOP-Mode Recovery (Figure 34 and Figure 35). All bits

are Write-Only, except bit 7, which is Read-Only. Bit 7 is a

flag bit that is hardware set on the condition of STOP re-

covery and reset by a power-on cycle. Bit 6 controls wheth-

er a low level or a high level is required from the recovery

source. Bit 5 controls the reset delay after recovery. Bits 2,

3, and 4, or the SMR Register, specify the source of the

STOP-Mode Recovery signal. Bits 0 and 1 determine the

timeout period of the WDT. The SMR Register is located in

Bank F of the Expanded Register Group at address 0BH.

When the Stop-Mode Recovery sources are selected in

this register, then SMR2 Register bits D0,D1 must be set

to 0.

SCLK/TCLK Divide-by-16 Select (D0).

D0 of the SMR

controls a divide-by-16 prescaler of SCLK/TCLK. The

control selectively reduces device power consumption

during normal processor execution (SCLK control) and/or

HALT mode (where TCLK sources counter/timers and

interrupt logic). This bit is reset to D0 = 0 after a Stop-Mode

Recovery, WDT Timeout, and POR.

External Clock Divide-by-Two (D1).

This bit can elimi-

nate the oscillator divide-by-two circuitry. When this bit is

0, the System Clock (SCLK) and Timer Clock (TCLK) are

equal to the external clock frequency divided by two. The

SCLK/TCLK is equal to the external clock frequency when

this bit is set (D1=1). Using this bit together with D7 of

PCON further helps lower EMI (that is, D7 (PCON) = 0, D1

(SMR) = 1). The default setting is zero. Maximum external

clock frequency is 4 MHz when SMR Bit D1 = 1 where

SCLK/TCLK = XTAL.

FF

6F

NOP

STOP

; clear the pipeline

; enter STOP mode

or

; clear the pipeline

; enter HALT mode

FF

7F

NOP

HALT

Figure 34. STOP-Mode Recovery Register (Write-

Only Except Bit D7, Which Is Read-Only)

D7

D6 D5

D4

D3

D2

D1

D0

SMR (FH) 0B

SCLK/TCLK Divide-by-16

0 OFF* *

1 ON

Stop-Mode Recovery Source

000 POR Only and/or External Reset*

001 Reserved

010 P31

011 P32

100 P33

101 P27

110 P2 NOR 0-3

111 P2 NOR 0-7

Stop Delay

0 OFF

1 ON

Stop Recovery Level

0 Low *

1 High

Stop Flag (Read-Only)

0 POR

1 Stop Recovery

Note: Not used in conjunction with SMR2

Source

* Default Setting After RESET

** Default setting after RESET and

Stop-Mode Recovery

*

*

External Clock Divide-by-2

0 SCLK/TCLK = XTAL/2*

1 SCLK/TCLK = XTAL

Figure 35. Stop-Mode Recovery Register 2

([0F] DH: Write-Only)

Figure 36. SCLK Circuit

D7

D6

D5

D4

D3

D2

D1

D0

SMR2 (0F) DH

Note: Not used in conjunction with SMR Source

Stop-Mode Recovery Source 2

00 POR only*

01 AND P20,P21,P22,P23

10 AND P20,P21,P22,P23,

P24,P25,P26,P27

Reserved (Must be 0)

SMR, D0

÷

2

÷

16

OSC

SCLK

TCLK

SMR, D1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| Z86C8416PEC | Z8 MCU MICROCONTROLLERS |

| Z86C8416PSC | Z8 MCU MICROCONTROLLERS |

| Z86C8416SEC | Z8 MCU MICROCONTROLLERS |

| Z86C8416SSC | Z8 MCU MICROCONTROLLERS |

| Z86C8416VEC | Z8 MCU MICROCONTROLLERS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| Z86C84 | 制造商:ZILOG 制造商全稱:ZILOG 功能描述:Z8 MCU MICROCONTROLLERS |

| Z86C8401ZEM | 功能描述:仿真器/模擬器 Z8 In-Circuit Em-C84 RoHS:否 制造商:Blackhawk 產(chǎn)品:System Trace Emulators 工具用于評估:C6000, C5000, C2000, OMAP, DAVINCI, SITARA, TMS470, TMS570, ARM 7/9, ARM Cortex A8/R4/M3 用于:XDS560v2 |

| Z86C8416PEC | 制造商:ZILOG 制造商全稱:ZILOG 功能描述:Z8 MCU MICROCONTROLLERS |

| Z86C8416PSC | 制造商:ZILOG 制造商全稱:ZILOG 功能描述:Z8 MCU MICROCONTROLLERS |

| Z86C8416SEC | 制造商:ZILOG 制造商全稱:ZILOG 功能描述:Z8 MCU MICROCONTROLLERS |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。