- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373785 > ZL49030DDA (ZARLINK SEMICONDUCTOR INC) Wide Dynamic Range DTMF Receiver PDF資料下載

參數(shù)資料

| 型號: | ZL49030DDA |

| 廠商: | ZARLINK SEMICONDUCTOR INC |

| 元件分類: | 信令電路 |

| 英文描述: | Wide Dynamic Range DTMF Receiver |

| 中文描述: | TELECOM, DTMF SIGNALING CIRCUIT, PDSO20 |

| 封裝: | 5.30 MM, MO-150AE, SSOP-20 |

| 文件頁數(shù): | 2/14頁 |

| 文件大小: | 353K |

| 代理商: | ZL49030DDA |

ZL49010/1, ZL49020/1, ZL49030/1

Data Sheet

2

Zarlink Semiconductor Inc.

detector circuit indicates the cadence (i.e., envelope) of the tone burst. The cadence information can then be

processed by an external microcontroller to identify specific call progress signals. The ZL4902x and ZL4903x can

be used with a crystal or a ceramic resonator without additional components. A power-down option is provided for

the ZL4901x and ZL4903x.

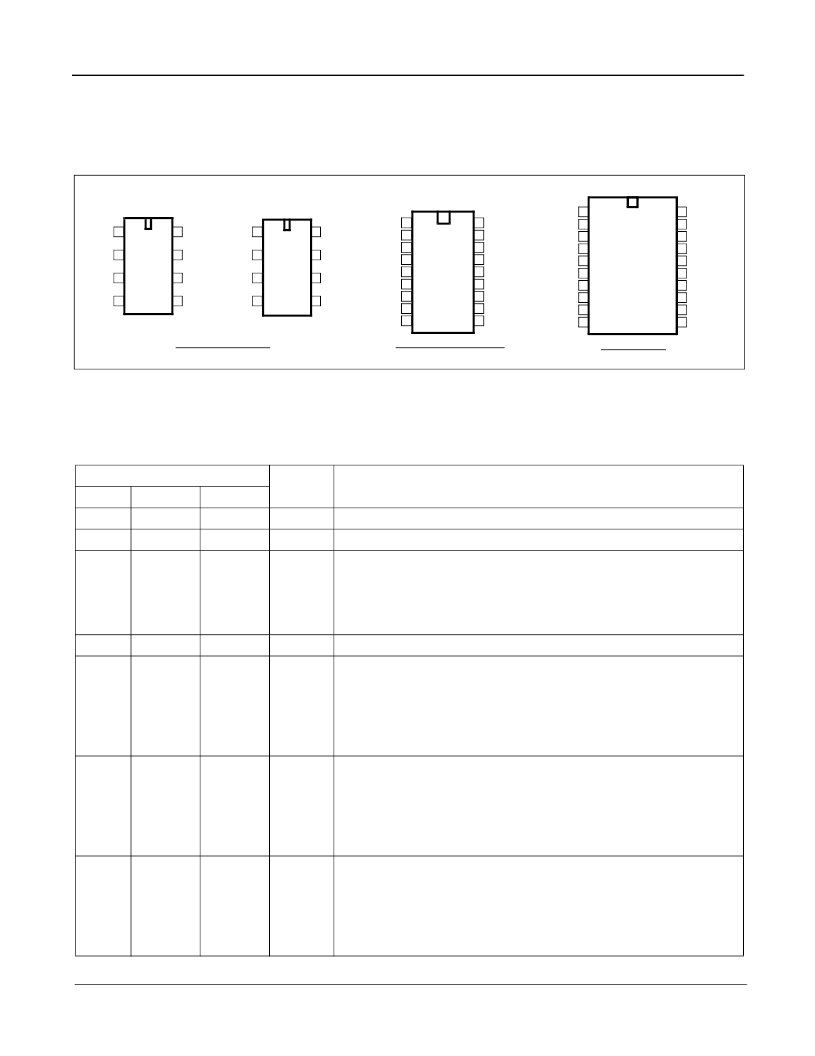

Figure 2 - Pin Connections

Pin Description

Pin #

4902x

1

2

3

Name

Description

4903x

2

4

6

4901x

1

-

3

INPUT

OSC2

OSC1

(CLK)

DTMF/CP Input.

Input signal must be AC coupled via capacitor.

Oscillator Output.

Oscillator/Clock Input.

This pin can either be driven by:

1)

an external digital clock with defined input logic levels. OSC2

should be left open.

2)

connecting a crystal or ceramic resonator between OSC1 and

OSC2 pins.

Ground.

(0V)

Serial Data/Call Progress Output.

This pin serves the dual function

of being the serial data output when clock pulses are applied after

validation of DTMF signal, and also indicates the cadence of call

progress input. As DTMF signal lies in the same frequency band as

call progress signal, this pin may toggle for DTMF input. The SD pin

is at logic low in powerdown state.

Acknowledge Pulse Input.

After ESt or DStD is high, applying a

sequence of four pulses on this pin will then shift out four bits on the

SD pin, representing the decoded DTMF digit. The rising edge of the

first clock is used to latch the 4-bit data prior to shifting. This pin is

pulled down internally. The idle state of the ACK signal should be

low.

Early Steering Output.

A logic high on ESt indicates that a DTMF

signal is present. ESt is at logic low in powerdown state.

9

11

4

5

4

5

V

SS

SD

13

6

6

ACK

15

7

7

ESt

(ZL490x0)

DStD

(ZL490x1)

Delayed Steering Output.

A logic high on DStD indicates that a

valid DTMF digit has been detected. DStD is at logic low in

powerdown state.

10

18

17

16

15

14

13

12

11

VDD

NC

NC

ESt/DStD

NC

ACK

NC

SD

NC

1

2

3

4

5

6

7

8

9

NC

INPUT

PWDN

OSC2

NC

OSC1

NC

NC

VSS

INPUT

PWDN

CLK

VSS

VDD

ESt/

DStD

ACK

SD

INPUT

OSC2

OSC1

VSS

VDD

ESt/

DStD

ACK

SD

ZL49010/1

ZL49020/1

ZL49030/1

8 PIN PLASTIC DIP

18 PIN PLASTIC SOIC

1

2

3

4

8

7

6

5

1

2

3

4

8

7

6

5

1

2

3

4

5

6

7

8

9

10

11

12

20

19

18

17

16

15

14

13

NC

NC

INPUT

PWDN

NC

NC

NC

OSC1

VSS

OSC2

20 PIN SSOP

NC

VDD

NC

ESt/DStD

NC

ACK

SD

NC

NC

ZL49030/1

NC

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ZL49030DDB | Wide Dynamic Range DTMF Receiver |

| ZL50012 | Flexible 512-ch Digital Switch |

| ZL50015 | Enhanced 1 K Digital Switch with Stratum 4E DPLL |

| ZL50015GAC | Enhanced 1 K Digital Switch with Stratum 4E DPLL |

| ZL50015QCC | Enhanced 1 K Digital Switch with Stratum 4E DPLL |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ZL49030DDB | 制造商:Microsemi Corporation 功能描述:DTMF RX 3.579MHZ 5V 20SSOP - Tape and Reel |

| ZL49030DDE1 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Wide Dynamic Range DTMF Receiver |

| ZL49030DDF1 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Wide Dynamic Range DTMF Receiver |

| ZL49031 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Wide Dynamic Range DTMF Receiver |

| ZL49031DCA | 制造商:Microsemi Corporation 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。