- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382783 > μPD30121 (NEC Corp.) 64-Bit MIPS RISC Microprocessor(64 位RISC 微處理器) PDF資料下載

參數(shù)資料

| 型號: | μPD30121 |

| 廠商: | NEC Corp. |

| 英文描述: | 64-Bit MIPS RISC Microprocessor(64 位RISC 微處理器) |

| 中文描述: | 64位MIPS RISC微處理器(64位的RISC微處理器) |

| 文件頁數(shù): | 2/2頁 |

| 文件大小: | 21K |

| 代理商: | ΜPD30121 |

In North America:

No part of this document may be copied or reproduced in any form or by any means without

the prior written consent of NEC Electronics Inc. (NECEL). The information in this document is subject to change

without notice. All devices sold by NECEL are covered by the provisions appearing in NECEL Terms and

Conditions of Sales only. Including the limitation of liability, warranty, and patent provisions. NECEL makes no

warranty, express, statutory, implied or by description, regarding information set forth herein or regarding the

freedom of the described devices from patent infringement. NECEL assumes no responsibility for any errors that

may appear in this document. NECEL makes no commitments to update or to keep current information

contained in this document. The devices listed in this document are not suitable for use in applications such as,

but not limited to, aircraft control systems, aerospace equipment, submarine cables, nuclear reactor control

systems and life support systems. “Standard” quality grade devices are recommended for computers, office

equipment, communication equipment, test and measurement equipment, machine tools, industrial robots,

audio and visual equipment, and other consumer products. For automotive and transportation equipment, traffic

control systems, anti-disaster and anti-crime systems, it is recommended that the customer contact the

responsible NECEL salesperson to determine the reliability requirements for any such application and any cost

adder. NECEL does not recommend or approve use of any of its products in life support devices or systems or in

any application where failure could result in injury or death. If customers wish to use NECEL devices in

applications not intended by NECEL, customer must contact the responsible NECEL sales people to determine

NECEL's willingness to support a given application.

For literature, call

1-800-366-9782

7 a.m. to 6 p.m. Pacific time

or FAX your request to

1-800-729-9288

or visit our web site at

www.nec.com

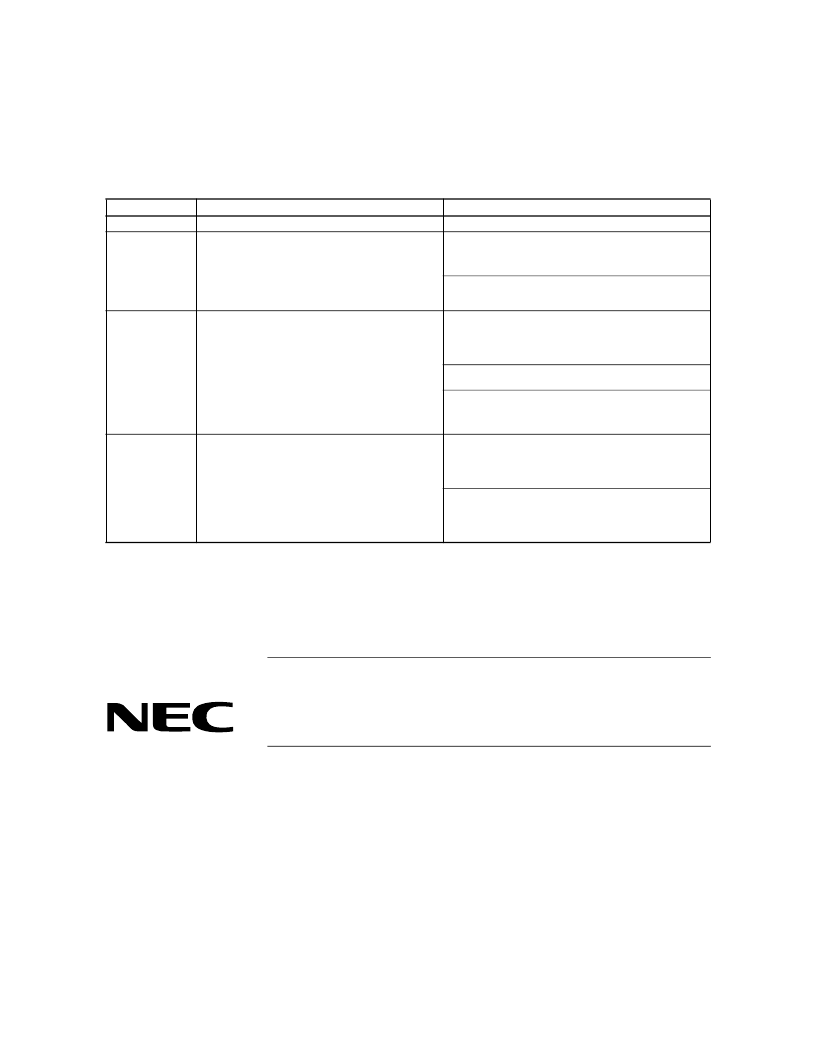

Table 3. Description of Power Modes

Mode

Clocks

Functions

Full speed

All internal clocks operate (including the bus clock).

All can be executed

Standby

All internal clocks, other than those provided to the internal

peripheral units and the internal timer/interrupt unit of the CPU

core, are fixed to a high level.

The V

R

4111 waits until the SysAD bus (internal) becomes idle after

the WB stage. The internal clock shuts down and the pipeline stops.

The PLL, timer/interrupt clock, internal bus clocks (TClock,

MasterOut), and RTC continue to operate.

The device returns to full-speed mode and an interrupt occurs. The

contents of bits indicating the states of pins in the peripheral units’

registers are undefined. The contents of other fields are retained.

Suspend

All internal clocks (including TClock), other than those supplied

to the real-time clock, interrupt control unit, power

management unit and to the timer/interrupt unit of the CPU,

are fixed to a high level.

The V

R

4111 waits until the SysAD bus (internal) becomes idle after

the WB stage, the DRAM enters self-refresh mode, and the

MPOWER pin becomes inactive. The internal clocks (including

TClock) shut down and the pipeline stops. The PLL, timer/interrupt

clock, MasterOut, and the real-time clock continue to operate.

If the SUSPEND instruction is executed during DMA transfer, the

DRAM transfer is suspended and the operation is undefined.

The processor switches from suspend to full-speed mode when an

interrupt request from the peripheral units or any reset occurs. The

contents of bits indicating the states of pins in the peripheral units’

registers are undefined. The contents of other fields are retained.

Hibernate

All internal clocks, other than those supplied to the real-time

clock, interrupt control unit, power management unit and CPU

core, are fixed to a high level.

The V

R

4111 waits until the SysAD bus (internal) becomes idle after

the WB stage, the DRAM enters self-refresh mode, and MPOWER

becomes inactive. The internal clocks (including TClock and

MasterOut) shut down, the pipeline and PLL stop, and the RTC

continues to operate.

The processor returns to full-speed mode when it is alarmed from

the real-time clock, the power on switch is pressed, or DCD# is

asserted. At this time, the contents of bits indicating the states of

pins in the peripheral unit’s registers and caches in the CPU core are

undefined. The contents of the other fields are retained.

NEC Electronics Inc.

CORPORATE HEADQUARTERS

2880 Scott Boulevard

Santa Clara, CA 95050-2554

TEL 408-588-6000

V

R

Series, V

R

4100, V

R

4101, V

R

4102, and V

R

4111 are either registered trademarks or trademarks of

NEC Corporation in the United States and/or other countries. Windows and Windows CE are either

registered trademarks or trademarks of Microsoft Corporation in the United States and/or other countries.

MIPS is a registered trademark of the MIPS Technologies, Inc.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| μPD30122 | 64-Bit RISC Microprosessor(64位RISC微處理器) |

| μPD30181 | 64-Bit RISC Microprosessor(64位RISC微處理器) |

| μPD30210 | 64-Bit MIPS RISC Microprocessor(64位MIPS RISC 微處理器) |

| μPD30200 | High-Performance, 64-Bit RISC Microprosessor(高性能64位RISC微處理器) |

| μPD30700L | 64-Bit Microprocessor(64位RISC微處理器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PD301-300-03-PC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

| PD301-300-03-P-C-200 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DC to DC Converter |

| PD301-300-03-P-C-250 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DC to DC Converter |

| PD301-300-03-P-C-300 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DC to DC Converter |

| PD301-300-03-PI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。