- 您現在的位置:買賣IC網 > PDF目錄382791 > μPD98401A (NEC Corp.) ATM SAR Chip(高性能異步傳輸模式控制器) PDF資料下載

參數資料

| 型號: | μPD98401A |

| 廠商: | NEC Corp. |

| 英文描述: | ATM SAR Chip(高性能異步傳輸模式控制器) |

| 中文描述: | 自動柜員機特區(qū)芯片(高性能異步傳輸模式控制器) |

| 文件頁數: | 3/4頁 |

| 文件大小: | 29K |

| 代理商: | ΜPD98401A |

When an ATM cell is received, the μPD98401A receive

circuitry verifies whether the cell belongs to one of the

selected receive channels by comparing the cell’s VPI/VCI

field against a lookup table maintained in control memory. If a

match is successful, the cell is directed to an integrated

receive FIFO.

The receive circuitry reads the channel corresponding entries

off the VC table. If this is the first received cell of a packet

and no buffer descriptors have been assigned or the buffer

has been exhausted, the receive circuitry fetches a new

R E C E I V E O P E R A T I O N

batch of free buffer descriptors and then moves the received

data (cell without the header) into the buffer location in sys-

tem memory pointed to by the first descriptor.

The receive circuitry increments the write pointer and

updates the CRC and the packet length entries. Upon

receiving a cell with end-of-packet indication, the receive cir-

cuitry verifies the packet length and the CRC calculation with

the value embedded in the last cell, writes a receive indica-

tion and error information into a receive mailbox in system

memory, and sends an interrupt (if enabled) to the host.

Voice

Data

Video

98YL-0166B (6/98)

ATM

Layer

Voice

Data

Video

μ

PD98404

μ

PD98401A

Adaptation

Layer

Physical

Layer

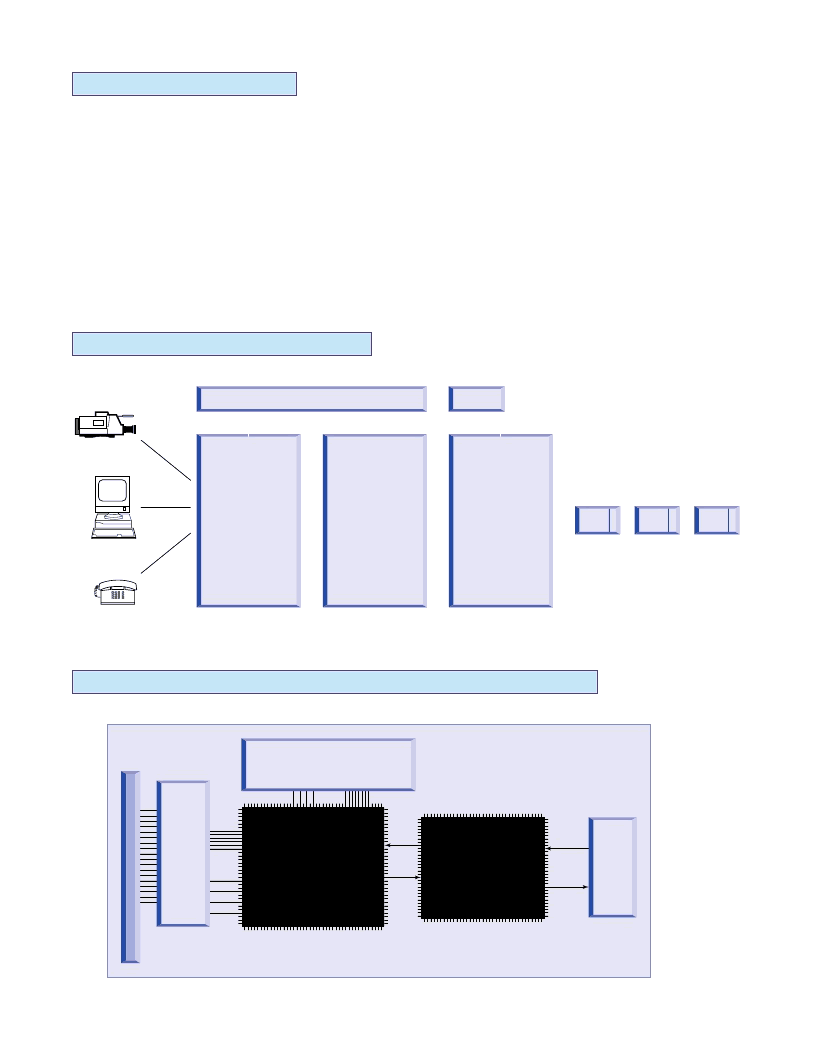

A T M S Y S T E M A R C H I T E C T U R E

T Y P I C A L A T M N E T W O R K I N T E R F A C E C A R D ( A T M - N I C )

Fiber

or

UTP

S-Bus/

PCI/

VME/

Others

98YL-0167B (6/98)

ATM

Controller

μ

PD98401A

ATM/SONET

PHY

μ

PD98404

Bus

I/F

PHY

I/F

Control Memory

相關PDF資料 |

PDF描述 |

|---|---|

| μPDPD30101 | 64-Bit Micro[rocessor(64位微處理器) |

| μPG2106TB | L-Band PA Driver Amplifier(L波段PA驅動器放大器) |

| μPG2110TB | L-Band PA Driver Amplifier(L波段PA驅動器放大器) |

| 1.5KE120A | TRANSIENT VOLTAGE SUPPRESSOR |

| 1.5KE110A | Unidirectional and bidirectional Transient Voltage Suppressor Diodes |

相關代理商/技術參數 |

參數描述 |

|---|---|

| PD98CNT30QMU | 制造商:Carlo Gavazzi 功能描述:PHOTO TS PL 30M AC/DC NO+NC |

| PD9909-59 | 制造商:Philco/Philips 功能描述: |

| PD9930-51 | 制造商:Philco/Philips 功能描述: |

| PD9933-59 | 制造商:Philco/Philips 功能描述: |

| PD9941-59 | 制造商:Philco/Philips 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。