- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371392 > 24AA32A-P (Microchip Technology Inc.) 32K 1.8V I 2 C O Serial EEPROM PDF資料下載

參數(shù)資料

| 型號(hào): | 24AA32A-P |

| 廠商: | Microchip Technology Inc. |

| 英文描述: | 32K 1.8V I 2 C O Serial EEPROM |

| 中文描述: | 32K的1.8VI 2二氧化碳串行EEPROM |

| 文件頁數(shù): | 7/12頁 |

| 文件大?。?/td> | 79K |

| 代理商: | 24AA32A-P |

1996 Microchip Technology Inc.

Preliminary

DS21162B-page 7

24AA32A

5.0

ACKNOWLEDGE POLLING

Since the device will not acknowledge during a write

cycle, this can be used to determine when the cycle is

complete (this feature can be used to maximize bus

throughput). Once the stop condition for a write com-

mand has been issued from the master, the device ini-

tiates the internally timed write cycle. Acknowledge

Polling (ACK) can be initiated immediately. This

involves the master sending a start condition followed

by the control byte for a write command (R/W = 0). If the

device is still busy with the write cycle, then no ACK will

be returned. If the cycle is complete, then the device will

return the ACK and the master can then proceed with

the next read or write command. See Figure 5-1 for flow

diagram.

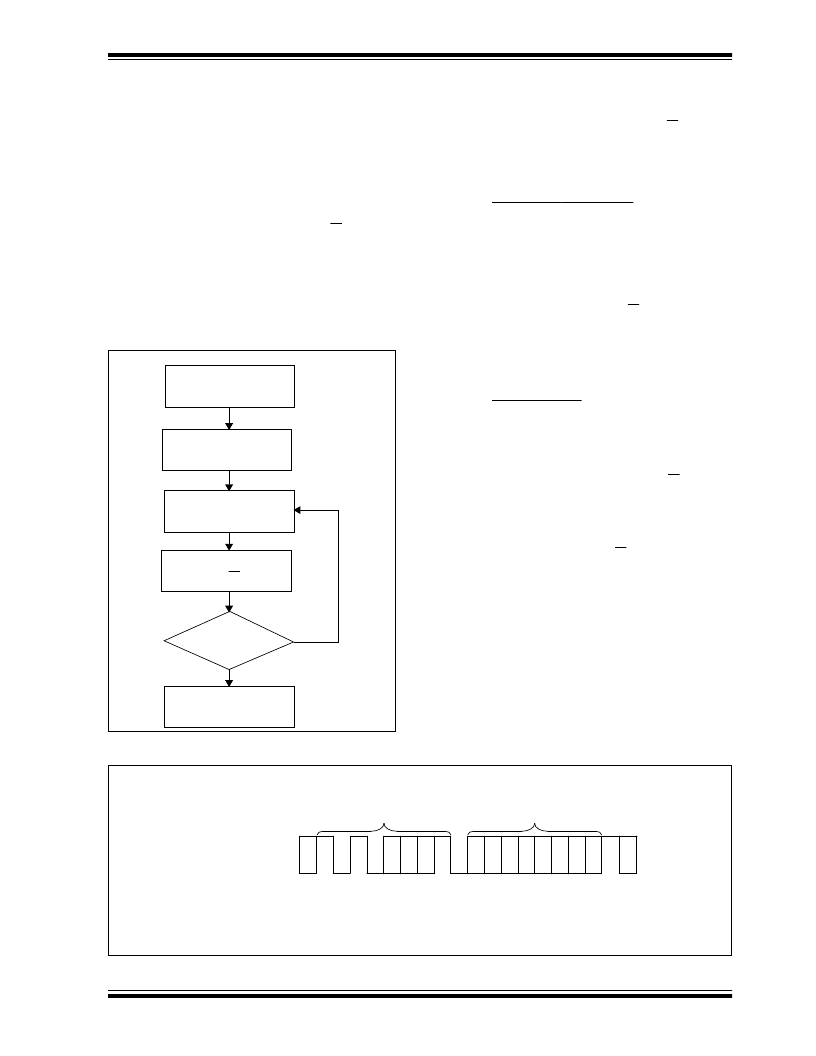

FIGURE 5-1:

ACKNOWLEDGE POLLING

FLOW

Send

Write Command

Send Stop

Condition to

Initiate Write Cycle

Send Start

Send Control Byte

with R/W = 0

Did Device

Acknowledge

(ACK = 0)

Next

Operation

NO

YES

6.0

READ OPERATION

Read operations are initiated in the same way as write

operations with the exception that the R/W bit of the

slave address is set to one. There are three basic types

of read operations: current address read, random read,

and sequential read.

6.1

Current Address Read

The 24AA32A contains an address counter that main-

tains the address of the last word accessed, internally

incremented by one. Therefore, if the previous access

(either a read or write operation) was to address n (n is

any legal address), the next current address read oper-

ation would access data from address n + 1. Upon

receipt of the slave address with R/W bit set to one, the

24AA32A issues an acknowledge and transmits the

eight bit data word. The master will not acknowledge

the transfer but does generate a stop condition and the

24AA32A discontinues transmission (Figure 6-1).

6.2

Random Read

Random read operations allow the master to access

any memory location in a random manner. To perform

this type of read operation, first the word address must

be set. This is done by sending the word address to the

24AA32A as part of a write operation (R/W bit set to

zero). After the word address is sent, the master gener-

ates a start condition following the acknowledge. This

terminates the write operation, but not before the inter-

nal address pointer is set. Then the master issues the

control byte again but with the R/W bit set to a one. The

24AA32A will then issue an acknowledge and transmit

the 8-bit data word. The master will not acknowledge

the transfer but does generate a stop condition which

causes the 24AA32A to discontinue transmission

(Figure 6-2).

FIGURE 6-1:

CURRENT ADDRESS READ

S

P

BUS ACTIVITY

MASTER

SDA LINE

BUS ACTIVITY

S

T

A

R

T

CONTROL BYTE

DATA BYTE

S

T

O

P

A

C

K

N

O

A

C

K

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 24AA32A-SM | 32K 1.8V I 2 C O Serial EEPROM |

| 24AA32A-SN | 32K 1.8V I 2 C O Serial EEPROM |

| 24AA32A-24LC32A | 32K I2C Serial EEPROM |

| 24AA32 | VCXO TCXO VCTCXO |

| 24AA32-P | 32K 1.8V I 2 C O Smart Serial EEPROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 24AA32ASC-I/S16K | 制造商:Microchip Technology Inc 功能描述:32K I2C SMARTCARD EE DIE IN WAFFLE PK - Gel-pak, waffle pack, wafer, diced wafer on film |

| 24AA32ASC-I/W16K | 制造商:Microchip Technology Inc 功能描述:32K I2C SMARTCARD EE WAFER - Gel-pak, waffle pack, wafer, diced wafer on film |

| 24AA32ASC-I/WF16K | 制造商:Microchip Technology Inc 功能描述:32K I2C SMARTCARD EE WFR ON FR - Gel-pak, waffle pack, wafer, diced wafer on film |

| 24AA32AT/SM | 功能描述:電可擦除可編程只讀存儲(chǔ)器 4kx8 RoHS:否 制造商:Atmel 存儲(chǔ)容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時(shí)鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| 24AA32AT/SN | 功能描述:電可擦除可編程只讀存儲(chǔ)器 4kx8 RoHS:否 制造商:Atmel 存儲(chǔ)容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時(shí)鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。